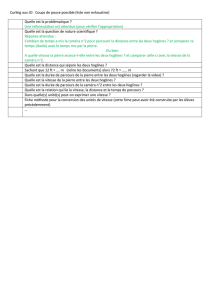

Sujets Stéphane Mancini

CSUG:SatelliteATISE

●NanoSatelliteétudiantpourmesurede

spectred'auroreboréaleetventsolaire

●Acquisition et pré-traitement des données

sur plate-forme Zynq

CollaborationCSUG/Pyxalis/RésolutionSpectra

2 coeur ARM Cortex A9

+

FPGA

ATISE

●Contexte

–Le projet ATISE a passé la phase 0 et le CNES a validé l'étude de faisabilité

–PhaseAduprojetdesatellite=>maquetteausolfonctionnelle

–Travailler dans un cadre « spatial »,dansleprocessus CNES, RNC version étudiante

–4 Octobre (aujourd'hui!!) : réunionétudiantsCSUG

–Mars 2017 :pointclé; Juillet 2017 revuedephaseAavecCNES

–PoursuiteenstagePFE

●Contraintes

–Environnementspatial=rayonnement=>durcissement

–Nano-satellite=>basse consommation

Plate-formedecalculFPGAZynqHW(FPGA)+SW(ARM) 100Gops/Watt⇒

●Objectifs

–Interfaceaucapteur«imageur»dePyxalis

–Algorithmesdepré-traitementetcalculscientifiqueàbord

●Réalisations

–Etuded'architectureetdeperformance

–Acquisitiondesdonnéesducapteurettestsenoptiqueclassique

–Pré-traitementsetcalculscientifiqueenHWetSW

–DéveloppementsHWensynthèsedehautniveau(HLS)

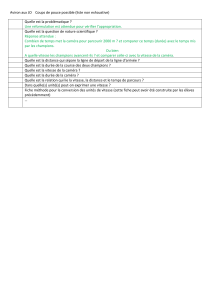

JPEG2000&HLS

SynthèseHLSd'uneunitédecompression

d'imageetvidéo.

Enéditionvidéo,ceformatestpréféréàMPEG2/4carilest

tolérantauxerreursetpermetl'accèsimmédiatàtouteimage

duflux.

http://research.microsoft.com/en-us/um/people/jinl/paper_2002/msri_jpeg.htm

JPEG2000&HLS

●Objectif

–Encoderdesimagesauplusprocheducapteurpourtransmission

–HLS=duHWàpartirduSW

●Spécifications

–NormeJPEG2000

●Réalisations

–Etuded'architecture

–C++ pour la HLSdepartiesdel'algorithme

–ValidationHLSparsimulation

–Mesuredeperformance :temps/surface

–IPsurplate-forme HW/SW Zynq

–Tests sur carteZybo

CaméraPan-optique

●Contexte

–Unecamérapan-optiqueoupanoramique

permetdeproduireunevueà360°àpartirde

prisesdevuemultiples

–Utiliserdesmodulescaméradetéléphone

mobileetfaireleraccordement(stitching)en

tempsréelsurFPGA

●Pointdedépart

–Algorithmedestitching

–Maquetteexistante

●Objectifs

–Calibrationdynamiquedelagéométrieet

luminosité

–Etuded'architecture

Caméra

RaspberryPi

Stitchingdes

4FOV

Différencesdegain

6

6

1

/

6

100%