TP N° 4 D`ELECTRONIQUE NUMERIQUE Technologie des

ROBERT Véronique

GE3

Année 2005-2006

TP N° 4 D’ELECTRONIQUE NUMERIQUE

Technologie des composants

Le but de ce TP est d’étudier les caractéristiques électriques d’une même porte

logique réalisée dans différentes technologies. Dans une première partie, nous

rechercherons la documentation technique de ces composants. Puis nous mesurerons

leurs performances électriques et pour finir nous verrons les problèmes d’interfaçage

entre les différentes familles.

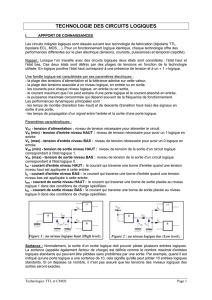

I) Préparation.

1) Caractéristiques des différentes portes :

La série standard date des années 60 ; elle a été introduite par Texas Instruments avec

le préfixe 54 / 74. La série 74 est une série civile contrairement à la série 54 qui est une série

militaire. La différence majeure se trouve au niveau des plages de températures et de tension

d’utilisation qui sont plus étendues pour le série militaire. Le boîtier 74000 contient 4 portes

NAND. Dans les séries, il existe deux familles de portes :

Famille TTL Famille CMOS

7400 74HC00

74LS00 74HCT00

74S00

74AS00

74ALS00

Pour la famille TTL, la commande se fait sur les courants ( absorption et injection de

courant), contrairement à la famille CMOS dont la commande se fait sur les tensions.

Famille TTL :

C’est une famille qui a été utilisée massivement, mais qui est peu à peu remplacée par

la famille CMOS. Les circuits TTL utilisent des transistors bipolaires en entrée et en sortie

(TTL = Transistor Transistor Logical).

Une porte TTL peut commander 10 TTL=sortance

7400

Cette porte NON ET, en TTL standard, possède une consommation et des temps de

basculement raisonnables. Aucune amélioration de technologie n’est présente sur cette porte.

La série standard offre un bon compromis entre vitesse et consommation. D’autre

séries ont été développées pour optimiser vitesse ou consommation puis des améliorations

technologiques ont permis d’accroître le produit vitesse – consommation.

74LS00 (Low Schottky)

Cette porte NON ET est une amélioration de la porte 7400. On utilise cette fois la

technologie Schottky. Dans cette série, on utilise les principes de la série 74S avec des

résistances plus élevées pour limiter la consommation. La consommation par porte est de

l’ordre de 2 mW et le retard de 9 ns.

On a changé un peu les caractéristiques pour moins consommer que les portes 74S00

et être plus rapide que les portes 7400.On augmente les valeurs des résistances pour réduire la

consommation Î temps de charge et de décharge plus long Î perte de vitesse

74S00 (Schottky)

On limite la saturation des transistors en montant des diodes Schottky. On diminue les

retards en associant des résistances plus faibles et un Darlington en place du transistor

d’injection. De plus, on met des diodes de protection en entrée. La consommation par porte

est de l’ordre de 20 mW et le retard moyen de 3 ns.

Comment est fabriquée une diode Schottky ?

Æ Caractéristique : plus rapide qu’une diode normale.

Æ Pourquoi ? on remplace le semi conducteur N par du métal. Le métal est un

matériau conducteur dans lequel il y a des électrons libres.

Dans le semi conducteur N, la quantité d’électrons libres va dépendre de la

quantité de dopage (ordre de grandeur : 1 atome dopant pour 1018 atomes

propres). Dans le métal M, il y a autant d’électrons libres que d’atomes de

métal. Les électrons sont donc en plus grands nombre dans M que dans N donc

ce sera plus rapide que la TTL Standard. L’inconvénient de cette solution est la

consommation plus importante qu’elle entraîne.

74AS00 et 74ALS00 (Advance Schottky)

Grâce à des avancées de la conception des circuits intégrés, les séries 74AS et 74ALS

sont plus rapides que les séries 74S. En terme de produit vitesse – consommation, ces séries

sont nettement meilleures.

Famille MOS et CMOS :

Dans cette technologie, on utilise des transistors MOS à enrichissement. Ces

transistors sont plus faciles à fabriquer et à intégrer, ils ont de petites dimensions et

consomment très peu. Les séries récentes surclassent les séries TTL pour les applications

courantes et la famille MOS ou CMOS devient la famille standard pour les circuits

numériques.

Avantage du MOS : le courant consommé par le dispositif est presque nul.

74HC00 :haute vitesse

Cette porte NON ET est réalisée en technologie CMOS. On constate que le temps de

basculement sont plus faibles que pour les autres portes. De plus la consommation reste moins

importante que pour une 7400. Cette consommation diminue considérablement si on utilise

plusieurs portes du composant.

Les retards de propagation de cette porte sont comparables à ceux de la série 74LS.

Par ailleurs, on a également augmenté les courants de sortie. La porte peut accepter des

tensions différentes : on travaille avec des 1 logiques qui ne sont plus à 5 V mais à 1,125 V.

On a diminué son niveau à cause de l’échauffement.

Inconvénient :on diminue les plages d’immunité au bruit.

74HCT00

Cette porte NON ET est une porte CMOS compatible avec des composants TTL. Les

temps de basculement et la consommation sont plus importants que pour le 74HC00, mais sa

comptabilité avec la technologie TTL est un réel avantage : les consommations restent

inférieures en CMOS.

Cette série, aussi rapide que la précédente, est compatible en tension avec les

dispositifs TTL. On peut utiliser dans un montage indifféremment les circuits TTL et CMOS

de la série HCT.

2) Tableau de mesures mettant en évidence les performances de différentes

technologies :

Famille TTL Famille CMOS

Paramètres 74 74LS 74AS 74ALS 74HC 74HCT

VIH(min) 2,0 V 2,0 V 2,0 V 2,0 V 3,5 V 2,0 V

VIL(max) 0,8 V 0,8 V 0,8 V 0,8 V 1,0 V 0,8 V

VOH(min) 2,4 V 2,7 V 2,7 V 2,7 V 4,9 V 4,9 V

VOL(max) 0,4 V 0,5 V 0,5 V 0,4 V 0,1 V 0,1 V

IIH(max) 40 µA 20 µA 200 µA 20 µA 1 µA 1 µA

IIL(max) 1,6 mA 0,4 mA 2 mA 100 µA 1 µA 1 µA

IOH(max) 0,4 mA 0,4 mA 2 mA 400 µA 4 mA 4 mA

IIL(max) 16 mA 8 mA 20 mA 8 mA 4 mA 4 mA

VIH : Voltage Input High: le niveau de tension minimum reconnu pour un 1 logique en entrée.

Toute tension inférieure n’est pas reconnue comme un niveau logique haut en entrée.

VIL : Voltage Input Low: le niveau de tension maximum reconnu pour un 0 logique en entrée.

Toute tension supérieure n’est pas reconnue comme un niveau logique bas en entrée.

VOH : Voltage Output High: le niveau de tension minimum garanti par le fabricant pour un 1

logique en sortie dans les conditions normales de charge.

VOL : Voltage Output Low: le niveau de tension maximum garanti par le fabricant pour un 0

logique en sortie.

IIH : Intensity Input High: l’intensité du courant qui traverse une entrée quand un niveau haut

est appliqué à cette entrée.

IIL : Intensity Input Low: l’intensité du courant qui traverse une entrée quand un niveau bas

est appliqué à cette entrée.

IOH : Intensity Output High: l’intensité du courant qui traverse la sortie quand elle est au

niveau haut dans des conditions de charges spécifiées.

IOL : Intensity Output Low: l’intensité du courant qui traverse la sortie quand elle est au

niveau bas dans des conditions de charges spécifiées.

Tableau comparatif entre certaines séries CMOS et TTL:

74 74S 74LS 74AS 74ALS 74HC

Consommation

par porte

statique (mW)

10 20 2 8 1,2

2,5 × 10-3

Consommation

par porte à

100kHz (mW)

10 20 2 8 1,2 0,17

Retard de

propagation

(ns)

9 3 9,5 1,7 4 8

Vitesse-

consommation

(à 100 kHz,pJ)

90 60 19 13,6 4,8 1,4

Fréquence

d’horloge maxi

(MHz)

35 12,5 45 200 70 40

Marge aux

bruits (cas

pessimistes)

0,4 0,3 0,3 0,3 0,4 0,9

Famille TTL

74 74LS 74S 74AS 74ALS

Valeurs nominales de performance

Retard de

propagation 9 ns 9,5 ns 3 ns 1,7 ns 4 ns

Consommation 10 mW 2 mW 20 mW 8 mW 1,2 mW

Produit vitesse -

consommation 90 pJ 19 pJ 60 pJ 13,6 pJ 4,8 pJ

Fréquence

d’horloge max 35 MHz 45 MHz 125 MHz 200 MHz 70 MHz

Sortance 10 20 20 40 20

Paramètres de tension

VOH(min) 2,4 V 2,7 V 2,7 V 2,7 V 2,7 V

VOL(max) 0,4 V 0,5 V 0,5 V 0,5 V 0,4 V

VIH(min) 2,0 V 2,0 V 2,0 V 2,0 V 2,0 V

VIL(max) 0,8 V 0,8 V 0,8 V 0,8 V 0,8 V

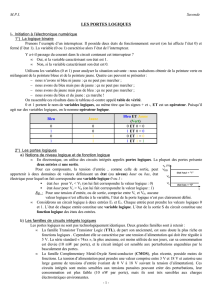

3) Structure TTL (NAND):

figure 1

Q1 est un transistor à double émetteur que l’on modélise par 3 diodes:

figure 2

D1 et D2 sont des diodes de protection, ou diodes de Clamping

D3 va créer une chute de tension supplémentaire qui empêche que les transistors Q3 et Q4

soient saturés en même temps, sinon VCC=5V serait relié à la masse

Table de vérité d’une porte NAND:

E1 E2 S

0 0 1

0 1 1

1 0 1

1 1 0

Si l’une des entrées, E1 ou E2, est à 0 (ou à 1) :

Æ pour pouvoir fixer entre E1 et E2 à la masse, il faut que le dispositif absorbe un courant.

Æ on n’a pas de courant dans D (cf fig 2), c’est à dire à la base de Q2

Æ Q2 et Q4 sont BLOQUES ce qui correspond à un circuit ouvert.

Æ Q3 est SATURE (présence d’un courant de base).

Æ D3 est passante.

Æ VS=VCC-VBE-VCEsat-R3I3

Æ Une sortie TTL à l’état haut va débiter du courant.

Le potentiel bas n’est pas à 0Æ dépend du potentiel de saturation

6

6

7

7

1

/

7

100%