2015-16.TD.td3-sujet.ado2016-11-07 09:27145 KB

Architecture des ordinateurs EFREI

1/4

TD 3

Réalisation du chemin des données d’une machine RISC

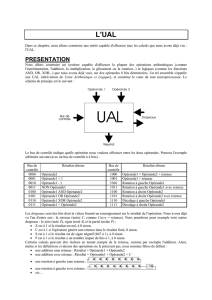

On cherche à réaliser une machine RISC très simple, pour cela, on doit d’abord déterminer le

chemin des données de la même manière que pour la petite machine CISC vue en cours

Le processeur que l’on veut schématiser possède 4 registres de données D0 à D3, et il s’agit

d’une machine à chargement/rangement.

Question 1) rappelez le principe d’une machine à chargement/rangement.

Voici le jeu d’instructions sommaire dont on veut disposer pour débuter : les instructions ont

en général 2 opérandes, et lorsqu’on lit une instruction, celle-ci se présente systématiquement

sous la forme : CODE, opérande source, opérande destination. Par exemple, ADD opérande1,

opérande2 effectuera : opérande2 = opérande1+opérande2 ; MOVE opérande1, opérande2

effectuera l’affectation opérande2=opérande1, etc…

Question 2) indiquez tous les types possible pour les opérandes des différents types

d’instructions listés ci-dessous :

Instruction de transfert (dont le nom est MOVE)

Ex : MOVE opérande1, opérande2

Instructions arithmétiques et logiques ADD, SUB, MUL, DIV, OR, AND, XOR, NOT

Ex : ADD opérande1, opérande2

Instruction de comparaison (dont le nom est CMP)

Ex : CMP opérande1,opérande2

L'instruction de comparaison agit de la manière suivante : pour savoir si deux valeurs sont

égales, on peut effectuer la soustraction opérande2 = opérande1 – opérande2 : si le résultat est

nul, c'est que les deux valeurs sont égales, et cela sera signalé par le flag Z, qui sera

positionné à 1. Cependant, l'opérande2 est modifiée par le calcul. L'instruction CMP effectue

la soustraction sans affecter le résultat à l'opérande2, mais modifie tout de même les flags.

Architecture des ordinateurs EFREI

2/4

Instructions de sauts (BRA, BRZ, BRN, BRC)

BRA : BRanch Always : branchement inconditionnel

BRZ : BRanch on Zero : branchement si le flag Z est à 1

BRN : BRanch on Negative : branchement si le flag N est à 1

BRC : BRanch on Carry : branchement si le flag C (retenue) est à 1

Ex : BRA opérande1

Question 3) Pendant le traitement d’une instruction par un processeur, lors de quelles phases

peut-il y avoir des accès à la mémoire ?

Lorsque l’on utilise une machine RISC, il faut séparer les différents accès mémoire

intervenant lors de phases distinctes. Ainsi en phase FETCH, on sait que l’on accède

forcément à une instruction qui doit être amenée dans le registre IR du processeur : on

considère alors que l’on accède à une mémoire contenant seulement les instructions.

Question 4) Comment pouvez-vous schématiser, le plus simplement possible, le chemin des

données de la phase FETCH, en utilisant les registres PC, IR ainsi que la mémoire contenant

les instructions ?

Question 5) En reprenant les types d’opérande listés dans la question 2, indiquez quelles sont

les valeurs qui peuvent être présentes à l’entrée de l’UAL. Schématisez ce chemin des données

en matérialisant les 4 registres individuellement ainsi que l’UAL.

Question 6) toujours en reprenant la question 2, d’où peuvent provenir les valeurs que l’on

peut stocker dans des registres de données ? Complétez le chemin des données correspondant.

Question 7) Les accès en mémoire sont possibles en phase EXECUTE. Indiquez à quelle

occasion ces accès ont lieu. On considère dans ce cas que ces accès se font dans une partie de

la mémoire différente de celle où sont stockées les instructions : une petite mémoire de

données. Ajoutez cette mémoire sur le schéma et indiquez le chemin des données relatif à

cette mémoire de données.

Architecture des ordinateurs EFREI

3/4

Question 8) Gestion du registre PC : on utilise, pour la gestion du registre PC, un simple

circuit additionneur à matérialiser sur le schéma. Quelles valeurs peuvent se trouver en entrée

de ce circuit additionneur ? complétez le schéma : vous avez une petite machine RISC !

Question 9) Utilité de l’unité de contrôle : Sans entrer dans le détail du fonctionnement de

cette unité, on veut décrire son rôle dans la gestion du chemin des données. Considérons

toutes les versions possibles de l’instruction de transfert MOVE : pour chacune de ces

versions, indiquez où doivent être dirigées les valeurs contenues dans les champs opérande1

et opérande2 de ces instructions. Ces chemins sont-ils bien distincts ? Sachant que l’unité de

contrôle est un séquenceur câblé, qui ne se base que sur la partie OPCODE de l’instruction

pour diriger les différentes valeurs dans le microprocesseur, combien de codes différents sont

nécessaires pour les différentes versions de l’instruction de transfert ?

Au total, combien de codes différents faut-il pour toutes les versions des instructions listées à

la question 2 ? En déduire le nombre de bits du champ OPCODE d’une l’instruction.

Question 10) En allant un peu plus dans le détail, on peut décrire le fonctionnement d’une

instruction en indiquant le rôle exact des opérandes. Prenons l’exemple de l’instruction :

MOVE adresse, registre : on peut la décrire de la façon suivante :

L’instruction, pointée par le registre PC, est lue dans la mémoire d’instructions et transférée

dans le registre IR.

La partie code est une version de l’instruction de transfert, elle est dirigée vers l’unité de

contrôle (le séquenceur) pour organiser le chemin des données.

La première opérande est une adresse, elle est dirigée vers un circuit décodeur pour indiquer

où se trouve effectivement la donnée en mémoire, une opération de lecture de la mémoire de

données est faite (c’est l’unité de contrôle qui gère cela).

La deuxième opérande est le numéro d’un registre, qui sera la destination de l’opération : un

circuit décodeur permet de sélectionner effectivement, parmi les 4, celui avec lequel aura lieu

l’opération. une opération d’écriture dans ce registre est effectuée.

L’UAL n’est pas sollicitée par cette instruction, les flags ne sont pas mis à jour.

Décrire de cette manière les trois instructions suivantes :

ADD #302, D3 : (addition d’une valeur immédiate)

CMP D2,D4

BRN –24

Architecture des ordinateurs EFREI

4/4

Question 11) On vous demande d’écrire un petit programme en assembleur, utilisant les

instructions de cette machine, pour trouver la valeur maximale parmi toutes les valeurs en

mémoire situées entre l’adresse 1000 et l’adresse 1100. Si vous essayez d’écrire ce

programme, à quelle difficulté vous trouvez-vous confronté ? Quel mode d’adressage serait

utile pour pouvoir traiter ce genre de problèmes ? Quelle partie du chemin de données est en

cause ? Proposez une modification du schéma obtenu pour permettre l’utilisation de ce mode

d’adressage. En supposant que l’on dispose maintenant de ce mode d’adressage, choisissez

une syntaxe pour ce type d’opérande et écrivez le programme demandé.

1

/

4

100%