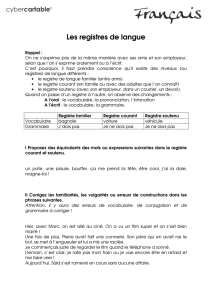

TP no 5 1 Introduction 2 Description 3 Jeu d`instructions

Univ. Lille 1 - Licence Informatique S3H 2ème année 2013-2014

Programmation

TP no5

1 Introduction

Ce tp porte sur les types sommes et le filtrage de motif. L’idée est de construire un assembleur,

un désassembleur et un simulateur d’une machine possédant une architecture 8 bits. Ce tp repose sur

un vieil exercice du cours d’Architecture. Le jeu d’instruction du microprocesseur a été entièrement

reproduit. Seules quelques mnémoniques ont été modifiée et quelques adaptations ont été effectuées

au niveau de la syntaxe. Cela a permis de rendre la syntaxe compatible avec celle de Caml. C’est

donc l’interprete ou le compilateur Caml qui va se charger de l’analyse syntaxique...

2 Description

La machine dispose de registres 8 bits : nommés de R0àR7. Il s’agit de registres généraux. Ces

registres peuvent être groupés par deux. Cela permet de disposer de 4registres 16 bits :nommés

RX0àRX3

3 Jeu d’instructions

On souhaite que notre microprocesseur dispose des instructions suivantes :

–ADD Rn, Rm— (pour ADD :-)) qui additionne la valeur du registre Rnavec la valeur du

registre Rmet stocke le résultat dans le registre Rn;

–AND Rn, Rm— qui fait la conjonction bit à bit des deux registres et range le résultat dans Rn;

–DEC Rn— (pour DECrement) qui soustrait 1à la valeur de Rnet stocke le résultat dans Rn;

–INC Rn— (pour INCrement) qui ajoute 1à la valeur de Rnet stocke le résultat dans Rn;

–NOT Rn— qui inverse bit à bit le registre Rnet qui y stocke le résultat ;

–LD Rn, HHLL — (pour LoaD) qui charge dans le registre Rnla valeur stockée en mémoire à

l’adresse (sur 16 bits) HHLL ;

–LDR0 RXn— qui charge la valeur du registre 0avec le contenu de la mémoire dont l’adresse

est définie par le registre RXn;

–MV Rn, Rm— (pour MoVe) qui charge dans le registre Rnla valeur contenu dans le registre Rm;

–MV Rn,arg — (pour MoVe) qui charge dans le registre Rnla valeur de l’argument “arg”.

L’argument est soit une valeur immédiate, soit un registre ;

–ST Rn, HHLL — (pour STore) qui stocke la valeur du registre Rnen mémoire à l’adresse

(sur 16 bits) HHLL ;

–STR0 RXn— qui stocke la valeur du registre 0en mémoire à l’adresse définie par le re-

gistre RXn;

–SUB Rn, Rm— (pour SUBstract) qui soustrait la valeur du registre Rmà la valeur du registre

Rnet stocke le résultat dans le registre Rn;

–SWP Rn, Rm— (pour SWaP) qui échange les valeurs contenues dans les registres Rnet Rm;

1

–JMP HHLL — (pour JuMP) qui effectue un branchement à l’adresse (sur 16 bits) HHLL ;

–JMP RXn— (pour JuMP) qui effectue un branchement à l’adresse définie par le registre RXn;

–JZ HHLL — (pour Jump if Zero) qui effectue un saut à l’adresse 16 bits HHLL si l’opération

précédente a donné un résultat nul ;

–JC HHLL — (pour Jump if Carry) qui effectue un saut à l’adresse 16 bits HHLL si l’opération

précédente a engendré une retenue ;

–NOP — (pour No Operation) qui est une instruction qui ne fait rien.

4 codage binaire des instructions assembleur

Opération Codage binaire Commentaire

NOP 0000 0000

JMP HHLL 0111 0000 - llll llll - hhhh hhhh hhhh hhhh correspond à HH

llll llll correspond à LL

JZ HHLL 0111 0001 - llll llll - hhhh hhhh hhhh hhhh correspond à HH

llll llll correspond à LL

JC HHLL 0111 0010 - llll llll - hhhh hhhh idem

ST Rn, HHLL 0100 0nnn - llll llll - hhhh hhhh nnn correspond au registre

hhhh hhhh correspond à HH

llll llll correspond à LL

LD Rn, HHLL 0100 1nnn - llll llll - hhhh hhhh idem

MV Rn,arg# 0101 0nnn - aaaa aaaa nnn correspond au registre

aaaa aaaa correspond à l’argument

DEC Rn0101 1nnn nnn correspond au numéro de registre

INC Rn0110 0nnn nnn correspond au numéro de registre

NOT Rn0110 1nnn nnn correspond au numéro de registre

ADD Rn, Rm100n nmmm 0nn correpond au premier registre

mmm correspond au deuxième registre

SUB Rn, Rm101n nmmm 0nn correpond au premier registre

mmm correspond au deuxième registre

AND Rn, Rm110n nmmm 0nn correpond au premier registre

mmm correspond au deuxième registre

SWP Rn, Rm111n nmmm 0nn correspond au premier registre

mmm correspond au deuxième registre

MV Rn, Rm00nn nmmm nnn correpond au premier registre

mmm correspond au deuxième registre

Reste : 0111 0011 et 0111 1***.

Il manque 3types d’instructions pour que le microprocesseur soit complet : ST en mémoire à

l’adresse donnée par un registre, LD en mémoire à l’adresse donnée par un registre et un JMP à une

adresse contenue dans un registre.

On profite des places restantes pour mettre ces instructions. On dénomme RX0 le registre 16

obtenu par la concaténation de R1 et R0 (R1 octet de poids fort), RX1 par R2 et R3,RX2 par R4

et R5 et RX3 par R6 et R7.

– 0111 0011 codera JMP RX0 ;

2

– 0111 10nn codera ST R0, RXn ;

– 0111 11nn codera LD R0, RXn.

5 materiel fourni

On fournit une archive contenant les fichiers suivants :

–

–

6 travail à faire

1. Récuperez l’archive.

2. Décompressez, lire tous les fichiers fournis,

3. Compilez et testez en lancant l’interprète.

4. On étend le jeu d’instruction de la manière suivante

– on ajoute une directive nommée LABEL suivie d’une chaine de caractère. Cette directive

n’est pas à proprement parler une véritable instruction. Elle sert à définir une étiquette,

qu’on pourra utiliser dans les instructions de saut.

– on ajoute trois instructions nommées JZl,JMPl et JCl suivies d’une chaine de caractères.

Elles permettent de sauter vers une étiquette. Faites ces modifications. Il sera commode

de fabriquer une table des symboles. Cette table possède comme type string*int array.

et contient pour chaque étiquette l’adresse mémoire correspondante. Cette table peut être

construite lors de la premiere phase.

voici un extrait du code étendu avec en début de ligne l’adresse courante et en commentaire

en fin de ligne la longueur de l’instruction.

0x0200: LD (R2, 0x100); (*longueur 3 octets *)

0x0203: LD (R3, 0x101); (*longueur 3 octets *)

0x0206: LD (R4, 0x102); (*longueur 3 octets *)

0x0209: LD (R5, 0x103); (*longueur 3 octets *)

0x020C: LABEL "boucle";

0X020C: LDR0 RX1; (*longueur 1 octet *)

0x020D: STR0 RX2; (*longueur 1 octet *)

0x020E: MOV (R1, 0x00); (*longueur 2 octets *)

0x0210: SUB (R0, R1); (*longueur 1 octet *)

0x0211: JZl "fin"; (*longueur 3 octets *)

0x0214: INC R2; (*longueur 1 octet *)

0x0215: JCl "incRX1"; (*longueur 3 octets *)

0x0218: LABEL "suite1";

0x0218: INC R4; (*longueur 1 octet *)

0x0219:...

le label "boucle" correspond à l’adresse 0x020C

le label "suite1" correspond à l’adresse 0x0217 ...

voici le genre de résultat que doit fournir phase1 après modification

0x027,[| ("boucle",0x20C);("suite1",0x0218);...;("fin",0x0227)|]

3

l’assemblage "à la main” du code donne

0x0200: 4A 00 01 LD (R2, 0x100); (*longueur 3 octets *)

0x0203: 4B 01 01 LD (R3, 0x101); (*longueur 3 octets *)

0x0206: 4C 02 01 LD (R4, 0x102); (*longueur 3 octets *)

0x0209: 4D 03 01 LD (R5, 0x103); (*longueur 3 octets *)

0x020C: LABEL "boucle";

0X020C: 7D LDR0 RX1; (*longueur 1 octet *)

0x020D: 7A STR0 RX2; (*longueur 1 octet *)

0x020E: 51 00 MOV (R1, 0x00); (*longueur 2 octets *)

0x0210: 81 SUB (R0, R1); (*longueur 1 octet *)

0x0211: 71 27 02 JZl "fin"; (*longueur 3 octets *)

0x0214: 62 INC R2; (*longueur 1 octet *)

0x0215: 72 1F 02 JCl "incRX1"; (*longueur 3 octets *)

0x0218: LABEL "suite1";

0x0218: 64 INC R4; (*longueur 1 octet *)

0x0219:...

le résultat fourni par assemble est donc

[|0x4A; 0x00; 0x01; 0x4B; 0x01; 0x01; 0x4C; 0x02;

0x01; 0x4D; 0x03; 0x01; 0x7D; 0x7A; 0x51; 0x00;

0x81; 0x71; 0x27; 0x02; 0x62; 0x72; 0x1F; 0x02;

0x64; ...|]

Elle doit être passée en paramétre à la fonction qui code les instructions. Le fichier exemple_etendu.ml

contient un code équivalent au fichier exemple.ml mais il est écrit avec le jeu d’instruction

étendu, il utilise des LABEL et des sauts vers des étiquettes.

4

1

/

4

100%