Etude en radiofréquences de transistors à effet de champ MOS

LA TECHNOLOGIE SOI 130 nm

45

Chapitre I : La technologie SOI 130 nm

L'introduction de ce mémoire présente, succinctement, plusieurs technologies disponibles

pour la réalisation de circuits analogiques micro-ondes. Pour des raisons de coût et de temps de

mise sur le marché, la technologie SOI devient une alternative économique aux systèmes réalisés

à base d'arséniure de gallium. Afin de mieux appréhender les qualités mais également les défauts

de la technologie Silicium-Sur-Isolant 130 nm, ce chapitre se propose de la présenter en

s'appuyant sur des résultats de mesure obtenus pour des MOSFET SOI partiellement désertés

polarisés en statique.

La première partie de ce chapitre décrit la technologie utilisée au cours de cette étude. La

distinction physique entre les MOSFET SOI complètement déserté et les MOSFET SOI

partiellement déserté est donnée afin d'introduire ce dernier. À partir des équations de base des

MOSFET sur substrat massif, transposables aux MOSFEST SOI partiellement déserté, la

seconde partie de ce chapitre détaille le comportement et la modélisation de ces dispositifs en

fonction de la polarisation statique. Dans cette partie, les phénomènes parasites sont également

abordés. La dernière partie de ce chapitre expose les effets physiques propre à la technologie SOI.

De part sa structure, la technologie Silicium-Sur-Isolant contient une zone isolante enterrée dans

le substrat. Par rapport à une technologie silicium sur substrat massif, celle-ci améliore la rapidité

du transistor en réduisant les effets capacitifs entre les régions drain/source et le substrat.

Cependant, la zone non désertée sous le canal est isolée du substrat et son potentiel est alors

flottant. Les conséquences sur le comportement du MOSFET SOI seront analysées dans cette

partie.

À noter que les transistors à effet de champ MOS considérés dans ce chapitre sont des

MOSFET à inversion avec un canal de type n. Pour les MOSFET à canal p, les effets physiques

sont globalement similaires.

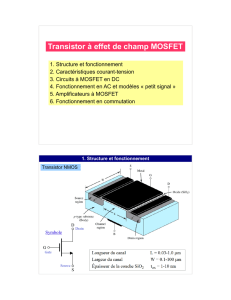

1. La technologie SOI

1.1. La désertion dans les MOSFET SOI

La structure interne des MOSFET en technologie SOI se différencie de celle des

MOSFET sur substrat massif par l’ajout d’une couche d'oxyde dans le substrat, voir figure 1-a.

Ainsi, cinq couches de matériaux composent le MOSFET SOI :

- les métallisations : contacts de grille, source et drain.

- l’oxyde de grille d'épaisseur tox.

- les régions source, ‛‛body” et drain, d'épaisseur tsi.

- l’oxyde enterré ou BOX, d'épaisseur tbox.

- le substrat.

CHAPITRE I

46

La photo de la figure 1-b montre une vue en coupe d'un MOSFET SOI en technologie

0,13 µm où ces différentes épaisseurs peuvent être identifiées aisément. Il est possible également

de distinguer les zones de siliciuration au niveau de la grille, de la source et du drain. Leur rôle est

de réduire les résistances de contact.

Figure 1 : a) Schéma d'un MOSFET SOI vu en coupe

parallèlement à la longueur du canal. b) Vue du MOSFET SOI au

microscope électronique à balayage.

La grille, l’oxyde de grille et le ‛‛body” forment une structure métal-isolant-

semiconducteur ou MIS, comme le substrat, l’oxyde enterré et le ‛‛body”. Par conséquent, deux

zones de charge d’espace sont présentes dans la zone active. Chacune de ces zones est

commandée par une grille : soit par la grille avant, soit par le substrat qui peut être assimilé à une

grille arrière. Chaque grille de la structure SOI impose un potentiel de surface à son interface

Si/SiO2 ainsi qu'un régime de fonctionnement : accumulation, désertion, inversion. Lorsque la

structure MIS fonctionne en régime d’inversion forte, l'épaisseur de la zone de désertion est

maximale[1]. Le potentiel de surface est pratiquement égal à 2·

φ

F où

φ

F est le potentiel de Fermi.

Dans ces conditions, les épaisseurs de chaque zone de désertion sont définies par l'équation (1).

max1,2

22

si f

d

a

xqN

ε

φ

⋅

=⋅ (1)

q est la charge des électrons, Na est la concentration des atomes donneurs du matériau et εsi est la

permittivité du silicium. À la figure 1, xdmax1 et xdmax2 représentent les valeurs maximales des

épaisseurs de chaque désertion dans la zone active, imposées respectivement par la grille avant et

par le substrat. Suivant les conditions de polarisation et de dopage, les deux zones de désertion

couvrent une partie ou la globalité du film de silicium de la zone active. Les conditions de

désertion en fonction de xdmax1 et xdmax2 sont résumées au tableau 1. Le MOSFET SOI est dit

complètement déserté ou ‛‛fully depleted” lorsque la zone de charge d'espace s'étend dans tout le

film de silicium. Sinon, le transistor est appelé partiellement déserté ou ‛‛partially depleted”.

Classiquement, l'épaisseur du film de silicium des MOSFET SOI partiellement déserté est de

l'ordre de 1000 Å, alors que celle des dispositifs complètement désertés est inférieure à 500 Å.

Toutefois, en fonction de la polarisation, le MOSFET SOI peut passer d'un état de désertion

partiel à un état de désertion complète et inversement.

Substrat

(g

rille arrière

)

xdmax1

V

gf

V

gb

p

+

n+ n+

Source Drain

xdmax2

Zone non

désertée

Canal

n- n-

a) b)

LDD

Oxyde de

grille

M

é

talli

s

ati

o

n

Grille

avant

Oxyde

enterré

Siliciuration

(

CoSi2

)

LA TECHNOLOGIE SOI 130 nm

47

Tableau 1 : Les différents régimes de fonctionnement du

MOSFET SOI en fonction des épaisseurs des zones de désertion.

Il est intéressant de noter que pour les MOSFET SOI complètement désertés, toute la

zone de désertion est entièrement contrôlée par la grille avant et la grille arrière, par

l'intermédiaire des capacités Cox1 et Cox2 respectivement. La figure 2 illustre le schéma équivalent

capacitif du MOSFET SOI complètement déserté.

Figure 2 : Schéma capacitif équivalent du MOSFET SOI

complètement déserté d'après [2].

Vgf et Vgb correspondent respectivement aux potentiels de la grille avant et arrière. CSi et Csub sont

les capacités du film de silicium et du substrat. Cit1, Cit2, Cit3 sont des capacités liées aux états

d'interface. Ψs1, Ψs2 et Ψsub sont les potentiels de surface avant et arrière aux interfaces SiO2,avant/Si

et Si/SiO2,arrière, et le potentiel de surface à l'interface SiO2,arrière/substrat. Par ces couplages

capacitifs, Ψs1 et Ψs2 sont chacun dépendants des variations des potentiels de la grille avant et de

la grille arrière. À partir des équations de Poisson, H. K. Lim et J. G. Fossum ont développé un

modèle de caractéristiques de courant en fonction des conditions de désertion arrière et avant[3].

En conséquence, la modélisation des MOSFET SOI complètement désertés est plus difficile que

celle des MOSFET SOI partiellement désertés dont les équations sont similaires à celles des

MOSFET sur silicium massif. Néanmoins, il faut prendre en compte les variations du potentiel

de la zone non désertée, appelée également ‛‛body”. Un autre avantage des MOSFET SOI

partiellement désertés par rapport aux MOSFET SOI complètement désertés concerne leur

réalisation. La fabrication des MOSFET SOI partiellement désertés utilise une technologie

similaire aux transistors réalisés sur silicium massif. Leur conception est, donc, plus simple que

pour des MOSFET SOI complètement désertés dont il est nécessaire de réduire l'épaisseur du

film de silicium.

Ψ

s

2

CSi

Csub

V

gb

Ψ

sub

V

gf

Ψ

s

1

Cox1

Cit2

V

gf

V

gb

Grille

avant

Oxyde de grille

Cox2

Cit3

Cit1

Oxyde

enterré

Substrat

(g

rille arrière

)

t

si ? x

dmax1 & tsi ? x

dmax2 x

dmax1,2 < tsi < xdmax1+ xdmax2 t

si ? x

dmax1+ xdmax2

Film de silicium Complètement déserté Non totalement déserté

dépend des conditions de polarisation Partiellement déserté

CHAPITRE I

48

1.2. Description de la technologie

Lors de cette étude, deux technologies ont été étudiées.

La première est la technologie 0,25 µm développée au CEA-LETI à Grenoble. Cette

technologie a été le point de départ de ces travaux. Trois ou six niveaux de métallisation peuvent

être employés afin d'assurer les connexions. Les épaisseurs d'oxyde de grille, de silicium et

d'oxyde enterré sont respectivement de 45, 1000 et 4000 Å. Des zones de LDD, des poches ou

‛‛pockets” et un canal rétrograde sont implantés dans la zone active du transistor. L'isolation

latérale est une structure LOCOS. Les plaques de test étudiées sont fabriquées sur deux types de

résistivité de substrat. Le premier substrat est de résistivité classique. ρ est située entre 1 et 10 Ω.

Le second substrat est fabriqué de façon à former une structure fortement résistive avec ρ

supérieure à 10 kΩ.

La seconde technologie est issue de la technologie 0,13 µm de ST-Microelectronics. Deux

épaisseurs d'oxyde de grille sont disponibles. Elles sont de 20 et 68 Å. Les épaisseurs de silicium

et d'oxyde enterré sont respectivement de 1600 et 4000 Å. Des zones de LDD, des poches et un

canal rétrograde sont implantés dans le transistor. L'isolation latérale est une structure STI. Les

dispositifs disponibles sont des MOSFET SOI partiellement déserté à ‛‛body” flottant, à ‛‛body”

connecté et à ‛‛body” lié. La méthode de fabrication des tranches SOI en technologie 0,13 µm est

le procédé Smart-Cut®. Le contexte de fabrication de ces plaques a été évoqué en introduction de

ce manuscrit.

2. Le MOSFET

Comme il a été évoqué précédemment, la modélisation des MOSFET SOI partiellement

désertés repose sur les équations des MOSFET sur silicium massif. Ainsi, cette partie présente la

théorie générale du fonctionnement des transistors à effet de champ MOS sur substrat massif.

Les résultats obtenus pour les MOSFET SOI en technologie 0,13 µm illustreront les propos

avancés. Cette partie débute par le fonctionnement général, en statique, des MOSFET à canal

long et large, dopés uniformément. Ces hypothèses impliquent que les effets de bord, dans le

canal, sont négligeables. Ceux-ci seront étudiés, dans un second temps, pour des transistors de

faible dimension.

2.1. Le fonctionnement des MOSFET en statique

La grille, l'oxyde de grille, la source, le drain, la zone active dont le canal et le substrat

composent l'architecture classique d'un MOSFET sur substrat massif, voir figure 3-a. Les

potentiels appliqués sur la grille, Vg, et sur le substrat, Vb, modulent le type et la quantité des

porteurs présents dans la zone active, voir figure 3-b. En première approximation, la structure

‛‛grille/oxyde de grille/substrat” se comporte comme une capacité. La différence de potentiel

entre l'interface ‛‛oxyde de grille/substrat” et la zone neutre du substrat s'appelle le potentiel de

surface, ΨS. Ce potentiel varie suivant les conditions de polarisation de la grille et du substrat mais

aussi en fonction du champ électrique longitudinal au canal (potentiels de source et de drain). Le

potentiel, sous le canal, varie jusqu'à un seuil fixé dans la partie neutre du substrat.

LA TECHNOLOGIE SOI 130 nm

49

Figure 3 : Le MOSFET à canal n sur substrat massif. a) schéma du

transistor; b) illustration du potentiel distribué dans le transistor.

Vgb=Vg-Vb. Ψox correspond à la différence de potentiel entre les deux interfaces de l'oxyde de

grille. Les différences des travaux de sortie au niveau de la grille et du substrat sont représentées

par

φ

ms1 et

φ

ms2.

φ

ms=

φ

ms1+

φ

ms2. Dans la suite de ce paragraphe, l'étude de cette structure de type

Métal Isolant Semi-conducteur ou MIS est approfondie.

2.1.1. Les régimes de fonctionnement

Par supposition, aucun potentiel n'est appliqué sur la source et le drain. Six modes de

fonctionnement sont identifiables en fonction de Vgb

[4-7]. Sauf la condition de bandes plates et le

régime d'inversion modérée, ceux-ci sont représentés à la figure 4.

Figure 4 : Diagramme de bandes d'énergies pour un MOSFET à

canal n à désertion. MOSFET en régime a) accumulation; b)

désertion; c) inversion faible; d) inversion forte.

φ

ms1

qΨ

S

EF

EV

EI

EC

qVg<0

EFm

a)

Ψ

S

<0

qΨ

B

q

Ψ

S

qVg>0 EF

EV

EI

EC

EFm

b) 0<

Ψ

S

<

Ψ

B

qVg>0

qΨ

S

EF

EV

EI

EC

EFm

qΨ

B

c)

Ψ

B<

Ψ

S

<2

Ψ

B

qVg>0

qΨ

S

EF

EV

EI

EC

EFm

qΨ

B

d) 2ΨBΨS

oxyde méta

l

silicium

Substrat

V

g

n+ n+

Source Drain

Oxyde de grille

Canal

Grille

p

Ψ

S

Potentiel

Zone de

désertion

y

Ψ

S

Ψ

ox

V

gb

V

b

a) b)

φ

ms2

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

1

/

43

100%