Conception et exploitation des processeurs

Conception et exploitation des processeurs

Chargé de cours : Frédéric Pétrot

Équipe pédagogique :

Stéphane Mancini, Luc Michel, Olivier Muller,

Christophe Rippert, Sebastien Viardot

Année universitaire 2012-2013

Conception et exploitation des processeurs

Structure du cours

C1 Introduction aux langages d’assemblage

pour les ISA x86_64 et MIPS

C2 Présentation du projet CEP

C3 VHDL

C4 Conventions pour les appels de fonctions

en assembleur x86_64 et MIPS

2 / 20

Conception et exploitation des processeurs

Introduction

Plan

1Introduction

2De ... à ...

3Processeur

3 / 20

Notes

Notes

Notes

Conception et exploitation des processeurs

Introduction

Introduction

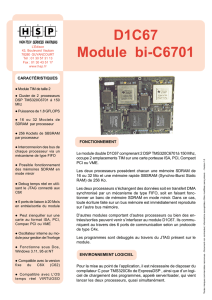

Objectif :

Conception d’un ordinateur minimaliste

Comprenant

un processeur

de la mémoire

des périphériques simples : LED, boutons

des périphériques moins simples : 7-segments, timer

des périphériques complexes : carte VGA, (joystick ?)

4 / 20

Conception et exploitation des processeurs

Introduction

Introduction

Challenge, ...

5 / 20

Conception et exploitation des processeurs

Introduction

Introduction

Comment ?

Conception du processeur

ISA : MIPS R3000

stratégie de conception : PC/PO

langage de conception : VHDL

sur les cartes Spartan de Xilinx

Notez bien : on ne part pas d’une feuille blanche, ...

Conception de l’environnement

utilisation de blocs existants : mémoire par ex.

conception de périphériques : VHDL

conception d’un « bus » permettant la connexion des

composants

6 / 20

Notes

Notes

Notes

Conception et exploitation des processeurs

De ... à ...

Plan

1Introduction

2De ... à ...

3Processeur

7 / 20

Conception et exploitation des processeurs

De ... à ...

Structure initiale

RESET

MMIPS_CPU.vhd

debugout

LEDs

RAM_PROG.vhd

addr

di

do

we

IP_DEBUG.vhd

addr

datain

we

dataout

ce

debugoutvalid

clk_gen.vhd

CLK50

CLK

1

32

8

32

32

32

1

1

8 / 20

Conception et exploitation des processeurs

De ... à ...

Quelques précisions

Mémoire RAM synchrone : ce n’est pas un bloc combinatoire !

Positionne addr => datain disponible au cycle suivant

Positionne addr/dataout/we=1 => dataout échantillonné clk ↑

Comportement registre, toujours lisible a

Bit ce inutile pour l’instant

a. sans lecture/écriture simultanée

entity RAM_PROG is

port (

clk : in std_logic;

-- 11 bits d’adresse

addr : in std_logic_vector(10 downto 0);

-- 32 bits de données

do : out std_logic_vector(31 downto 0);

di : in std_logic_vector(31 downto 0);

we : in std_logic

);

end RAM_PROG;

9 / 20

Notes

Notes

Notes

Conception et exploitation des processeurs

De ... à ...

Quelques précisions

Mémoire RAM synchrone

architecture Behavioral of RAM_PROG is

subtype mot is std_logic_vector(31 downto 0);

type zone_memoire is array (natural range 0 to 2048) of mot;

constant m0: zone_memoire :=(

0 => x"3c1cdead", -- lui $28,0xdead

1 => x"379cbeef", -- ori $28, $28, 0xbeef

others => x"ffffffff" --Reset

);

signal m: zone_memoire := m0;

begin

process(clk)

begin

if (clk’event AND clk=’1’) then

if we=’1’ then

m(conv_integer(addr)) <= di;

end if;

do <= m(conv_integer(addr));

end if;

end process;

end Behavioral;

10 / 20

Conception et exploitation des processeurs

De ... à ...

Structure finale

CLK

Reset

MMIPS_CPU.vhd

debugout

LEDs

MMIPS_et_environnement.vhd

IP_DEBUG.vhd

addr

datain

we

dataout

ce

debugoutvalid

RAM_PROG.vhd

addr

di

do

we

clk_gen.vhd

CLK50 CLK

IP_SWITCH.vhd

Interrupteurs

IP_7SEG.vhd

Afficheurs 7 segments

VGA.vhd

R

G

B

HS

VS

GeneRGB.vhd

GeneSync.vhd

doa

dia

addra

wea

RAM_VIDEO.vhd

addr

addr

addr

dout dout

dout

dout

din_switch

din_ram_prog

din_ram_video

we_ram_prog

we_ram_video

we_7seg

din_ram_prog din_ram_video

din_switch

we_7seg

we_ram_prog

we_ram_video

we_7seg

MMIPS_bus.vhd

11 / 20

Conception et exploitation des processeurs

De ... à ...

Quelques précisions

Bus pour accès différents composants : principes

Écriture combinatoire :

processeur positionne addr/dataout/we=1/ce=1

bus décode adresses pour calcul we_ram_prog,

we_ram_video,we_7seg (mutuellement exclusifs)

dataout échantillonné par composant avec we_... = 1 sur

clk ↑

Lecture séquentielle :

processeur positionne addr/datain/ce=1

sur clk ↑, composants produisent din_ram_prog,

din_switch,din_ram_video, bus échantillonne addr

bus utilise addr échantillonné pour décoder quel signal

din_... produire sur datain

12 / 20

Notes

Notes

Notes

Conception et exploitation des processeurs

Processeur

Plan

1Introduction

2De ... à ...

3Processeur

13 / 20

Conception et exploitation des processeurs

Processeur

Processeur

Caractéristiques globales de l’architecture :

bus de données et d’adresse sur 32 bits

taille de l’instruction : 32 bits

ISA 3-adresses

32 registres opérandes des instructions, noté $0 à$31

registres $1 à$30 : usage général

registre $0 : vaut toujours 0

registre $31 : contient adresse de retour de fonction (imposé

par 2 instructions)

registre pc : adresse de l’instruction suivante

registre ir : instruction en cours d’exécution

registres hi et lo : résultat multiplication ou division entière

14 / 20

Conception et exploitation des processeurs

Processeur

Rappel des formats

Où récupérer l’information dans l’instruction

registre

5 bits dans l’instruction

immédiat

5 bits dans l’instruction, pour les décalages

16 bits dans l’instruction, différentes interprétations possibles

26 bits dans l’instruction, pour les sauts inconditionnels

indirect registre (+ déplacement)

5 bits pour identifier le registre + 16 bits pour la constante

relatif à pc (2 cas)

15 / 20

Notes

Notes

Notes

6

6

7

7

1

/

7

100%