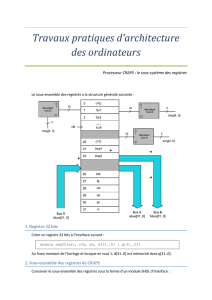

Chemin de données

Titre

2. 1

Chemin de données

Les composants qui permettent le stockage,

le transfert et la transformation des données.

Chemin de données

registre instruction IR

registre compteur PC

unité de contrôle

unité de

calcul

ensemble de

registres

+

PROGRAMME

DONNEES

MEMOIRE

Titre

2. 2

Chemin de données

1. Les composants du chemin de données

mémoire

centrale

unité

centrale

Stockage des

programmes et

des données

Traitement des

données

C P URAM

SYSTEM BUS

Chemin de données

Titre

2. 3

Chemin de données

Le chemin de données :

•Les composants qui traitent les données

–Mémoire centrale : instructions et données des programmes

–Registres internes :

•Registres généraux : données temporaires pour les calculs

•Registres de contrôle et d'état : informations de contrôle

nécessaires à l'exécution du programme

–Unités de calcul

–Bus

•La façon dont ces composants sont interconnectés

Titre

2. 4

Chemin de données

Mémoire instructions

Mémoire données

Cache instructions

Cache données

Registres entier Registres flottant

Calcul

entier 1

Calcul

entier 2

Calcul

float 1

Calcul

float 2

Ordonnancement des tâches

Cas général

Extraction des

instructions

Titre

2. 5

Chemin de données

instruction register

IR

program counter

PC

unité de contrôle

unité de

calcul

ensemble de

registres

+

PROGRAMME

DONNEES

MEMOIRE

Cas étudié

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

1

/

18

100%