Sujet de thèse CIFRE : Thématique fiabilité

Sujet de thèse CIFRE : Thématique fiabilité

« Etude des interactions électriques conduites sur des composants et

systèmes électroniques »

Introduction

Ce sujet s’inscrit dans le cadre des activités de recherche du LaMIPS (Laboratoire de

Microélectronique et Physique des Semi-conducteurs ». et plus particulièrement dans l’axe

de recherche portant sur la fiabilité des composants et systèmes électroniques.

La finalité de ce sujet est de compléter les outils de modélisation et de simulation dans les

domaines de fréquence, puissance et énergie correspondant aux évènements électriques

accidentels conduits de type décharge électrostatiques, surtension électrique regroupés sous

le nom EOS (Electrical Over Stress). Cette étude s’applique aux composants de protection,

aux circuits intégrés et aux systèmes électroniques.

Contexte

Une grande attention est dédiée, depuis plusieurs années, à la désensibilisation des

composants électroniques pour minimiser les effets destructifs dus aux phénomènes de

décharge électrostatique ESD, notamment en introduisant des circuits de protection interne.

Les chaînes de fabrication, elles aussi, ont bénéficié d’améliorations pour réduire le taux de

circuits défaillants liés à ces faits. Les évolutions technologiques et l’amélioration

permanente des protections contre les accidents de type décharge électrostatique ESD ont

laissé apparaitre un autre type de mécanisme de défaillance, que nous appellerons ici

interaction électrique conduite ou Over Voltage Stress (OVS), et qui devient la cause d’une

proportion de plus en plus importante de défauts de qualité et de fiabilité pour les fabricants

de composants et les assembleurs.

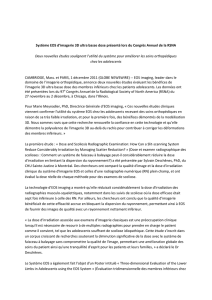

Les standards ESD actuels se rapportent à des domaines de test bien spécifiques en

durée et en quantité d’énergie (Fig. 1) qui ne couvrent qu’une partie des évènements de

type EOS. Dans un contexte global d’amélioration de la qualité et du zéro défaut demandé,

par exemple par le marché automobile, un nouveau besoin de renforcer la tenue des

composants à ce type de stress est impératif. En conséquence, il est nécessaire de prendre

en compte lors de la conception, la caractérisation et la qualification des composants, une

couverture de test élargie à ces phénomènes. Ceci pousse la communauté électronique

industrielle internationale à mettre en place de nouvelles méthodes standardisées ainsi que

de nouveaux équipements de test de type EOS puis à faire évoluer les standards actuels.

Pour cela, la société Presto Engineering a déjà commencé à mettre en place un

prototype expérimental de caractérisation dans le domaine EOS, le TPG (Transient Power

Generator). Ce banc expérimental a la possibilité de soumettre des circuits ou des

composants a des stress électriques conduits autres (fréquence, énergie…) que ceux décrits

dans les normes de test ESD et va permettre la mise en évidence des mécanismes de

défaillance consécutifs aux surtensions de nature OVS.

Fig. 1 Etat de l’art des standards EOS.

A plus long terme, la finalité de cette étude sera de proposer un standard EOS aux

fournisseurs et aux équipementiers pour améliorer la qualité des produits face à ces interactions.

Sujet

Le sujet proposé consistera à approfondir la compréhension des mécanismes de défaillance,

de vieillissement et les limites physiques des composants causés par des phénomènes EOS

de type non ESD et non Latch Up. Les principaux objectifs de cette étude sont de proposer

et valider de nouvelles méthodes de test EOS permettant de reproduire les dégradations

physiques observées lors de l’analyse de défaillance de circuits ou composants défectueux

dans le but d’accroître leurs performances.

Déroulement de la thèse

Les objectifs décrits précédemment feront appel à la fois à des travaux théoriques et

expérimentaux, les différentes étapes de la thèse sont envisagées de la façon suivante :

Le doctorant devra par une recherche bibliographique établir un état de l’art dans le

domaine EOS, il recensera les différentes normes et événements de surtension, surintensité,

over et undershoot, polarisation inverse…, sources d’agression des dispositifs, ainsi que la

nature des dégradations internes observées dans les composants et étudier les modèles

physiques associés à ces phénomènes.

L’acquisition de ces connaissances permettra d’établir les études de cas les plus

intéressantes et de définir les véhicules de tests associés.

Puis le candidat devra par des tests expérimentaux reproduire les conditions

critiques qui feront apparaître les modes de défaillances. Ces tests se feront à l’aide du banc

de mesures expérimental capable d’appliquer aux composants des impulsions électriques

paramétrables en tension, courant, durée, forme, temps de montée…. Ces expériences

Le vide à combler, objet de

l

’

étude

permettront d’établir des comparaisons entre les analyses de défaillance obtenues et les

dégradations les plus fréquemment rencontrées afin de déterminer et justifier les formes

d’ondes les plus représentatives.

La compréhension des mécanismes de dégradation permettra de vérifier la validité

des modèles existants et de les améliorer ainsi que de définir des méthodologies de tests

permettant d’augmenter la robustesse et les performances des composants, sous systèmes et

systèmes aux interactions électriques conduites.

Lieu

Les travaux se dérouleront principalement au sein du groupe R&D de la société

Presto Engineering située à Caen, le candidat sera intégré dans une équipe ayant plus de

vingt années d’expérience dans le domaine de la fiabilité. Le candidat sera également

amené à coopérer avec les équipes opérationnelles de fiabilité et analyse de défaillance de

Presto Engineering.

Profil recherché :

Bac + 5 ayant de bonnes connaissances en :

- Procédés de semi-conducteurs.

- Caractérisation et mesure électrique.

- Logiciel de simulation et de modélisation analogique

- Anglais courant

- Profil :

o Autonomie

o Curiosité

o Capacité à travailler dans un contexte international

Moyens/ressources

- Banc de mesure TPG (Transient Power Generator)

- Outils de modélisation et simulation analogique.

- Démonstrateurs :

o Composants de protection de système.

o Composants de protection de circuits intégrés.

o Composants de protection ou transistors de circuits intégrés.

Démarrage souhaité de la thèse : avril 2011

Contacts :

Scientifique : Patrick Martin, Maître de conférences, Enseignant chercheur, HDR

(02 31 06 27 26) (patrick.martin@univ-rouen.fr)

Industriel : Jean-Luc Lefebvre, Ingénieur PRESTO Engineering (02 31 06 27 14)

(jean-luc.lefe[email protected])

1

/

3

100%