am plificateurs de pu is s an ce

A l’aide d’un amplificateur de puissance, on cherche à transmettre un maximum de puissance à

une charge, généralement de faible impédance, telle un haut-parleur ou un moteur électrique.

C’est ici la notion de rendement énergétique

qui prédomine : la puissance (P

E

) fournie par la

commande est souvent négligeable ; la puissance

(P

U

) transmise à la charge provient de l’alimentation

continue qui polarise les éléments actifs internes.

Les courants mis en jeu au sein de l’étage sont

importants ; l’effet Joule qui en résulte oblige

à considérer l’échauffement des composants

et à dimensionner des systèmes de refroidisse-

ment (radiateurs, ventilateurs…)

Nous nous limiterons dans ce qui suit à la présentation d’amplificateurs de puissance de principe, réalisés

autour de transistors bipolaires. Les études envisagées seront aisément transposables à des structures plus

complexes, ou mettant en jeu des technologies plus actuelles (Étages intégrés, étages à transistors MOS,

IGBT…)

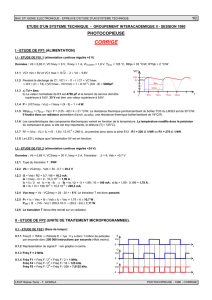

1 . Amplification de puissance en classe A

En classe A, il y a besoin d’un seul transistor pour réaliser

un étage amplificateur de signaux alternatifs.

Le transistor utilisé fonctionne dans la partie linéaire de ses

caractéristiques.

La position du point de repos sur la droite de charge

(idéalement au milieu, Cf. ci-contre), permet une excursion

importante du courant collecteur de part et d’autre sans

distorsion appréciable.

Malheureusement, la dissipation importante du transistor au

repos entraîne un piètre rendement pour ce type d’étage.

Commande Charge

Alimentation

continue

Étage de

puissance

P

alim

P

U

P

J

P

E

vCE

iC

IC0

VCE0

0

1.1 Étage à liaisons capacitives.

L’étage est de type émetteur commun.

Afin d’assurer un maximum de dynamique de sortie, le point

de repos est idéalement V

CE0

= V

CC

/2 et I

C0

= V

CC

/2R

C

.

La résistance de sortie de cet amplificateur est R

C

;

en conséquence, l’adaptation des impédances impose à la

charge R

U

de vérifier R

U

≈ R

C

.

Droites de charge : Au repos, le transistor « voit » une

charge R

C

; sa droite de charge statique a une pente de

(-1/R

C

).

Par contre, pour le régime dynamique, les résistances R

C

et R

U

≈ R

C

se retrouvent en parallèle et le transistor est

effectivement chargé par R

C

/2 ! (Cf. schéma ci dessous)

Il s’en suit une nette différence entre la droite de charge du transistor en statique et en dynamique, ce qui provoque

une limitation de la dynamique de sortie en tension à V

CC

/4.

Puissances au repos.

La puissance utile est nulle (présence de C

2

).

En négligeant I

B0

, l’alimentation fournit I

C0

sous V

CC

, soit

c

2

cc

0ccclima

R2

V

I.VP ≈=

Le transistor et R

C

dissipent chacun

c

2

cc

0c

cc

J

R4

V

I.

2

V

P

2

1≈≈

Par exemple, avec V

CC

= 15V et R

U

≈

R

C

= 8

Ω

, l’alimentation fournit une puissance de 14W en pure perte !

Puissances en régime dynamique.

Supposons la tension d’attaque u

E

(t) sinusoïdale et l’étage approximativement linéaire.

L’alimentation fournit un courant ondulé du type I

C0

+ Î

C

.sint sous la tension V

CC

, ce qui reste égal à V

CC

.I

C0

en

valeur moyenne .

En classe A, l’alimentation fournit la puissance

c

2

cc

lima

R2

V

P≈, quelque soit le niveau des signaux traités.

La charge R

U

≈ R

C

est soumise à la tension u

S

(t), dont la valeur de crête peut juste atteindre ¼ V

CC

(cf. plus haut)

La puissance de sortie,

u

2

S

u

R

U

P= , peut atteindre la valeur maximale

c

2

cc

u

2

cc

maxu

R32

V

R

1

.

24

V

P≈

≈

Le rendement de cet étage est ainsi

2

cc

s

c

2

cc

u

2

S

lima

u

V

U

2

R2

V

R

U

P

P

===η

; il croît avec le niveau de sortie, pour

atteindre au maximum 1/16 soit 6% environ.

Un tel étage en classe A, avec liaisons capacitives est totalement inadapté pour l’amplification de puissance !

Reprenons l’exemple numérique précédent (V

CC

= 15V et R

U

= 8

Ω

) : L’alimentation va fournir 14W, pour une

puissance utilisable en sortie de moins de 1W !!

C1

RC RB

C2

RU

+Vcc

0V

uE

iE

iS

uS

vCE

iC

c

cc

R2

V

Vcc/2

0

c

cc

R

V

Vcc

Dte de charge dynamique

Dte de charge statique

3Vcc/4

RB

r

ib

gmvbe

vbe

uE

uS

RC

RU

i

E

Pour le régime dynamique, le

transistor voit une charge R

C

/2

1.2 Étage à liaison par transformateur.

Un transformateur assure une isolation des composantes continues, mais il permet également de réaliser

l’adaptation des impédances en puissances, par un choix approprié de son rapport de transformation.

Le transformateur ci contre a un rapport de transformation m et il est

considéré comme idéal : m

I

I

U

U

2

1

1

2

==

Sa résistance d’entrée est

2

u

2i

u

ent

m

R

i

u

.

m

1

mi

m

u

R

2

2

2

2

1

1====

Le principe d’un tel étage est représenté à droite :

Le primaire du transformateur est placé au collecteur du

transistor ; son secondaire attaque la charge R

U

.

La résistance d’émetteur R

E

est nécessaire pour limiter le

courant collecteur de repos, mais elle doit être découplée pour

les signaux variables.

Nous supposerons donc le découplage parfait pour l’alternatif.

Le point de repos du transistor est, en classe A : V

CE0

= V

CC

/2

et I

C0

= V

CC

/(2R

E

)

La charge du transistor est constituée par R

E

en statique (repos)

et par la résistance d’entrée du transformateur chargé, soit

2

u

m

R

en dynamique.

Droites de charge.

Au repos : V

CE

= V

CC

– R

E

I

C

, soit une pente de

E

R

1

−

En dynamique : v

ce

= -R

U

/m

2

.i

c

Il en découle que la pente de la droite de charge dynamique du

transistor (

U

2

R

m

−) peut être ajustée par la valeur de m.

Nous obtiendrons ainsi les droites dynamiques (1) ou (2), selon

que

2

u

m

R

est respectivement inférieur ou supérieur à R

E

.

Or la puissance de sortie maximale est définie pour une

dynamique en tension et une dynamique en courant maximales,

sans déformation en régime sinusoïdal.

Il est clair que c’est le choix

E

2

u

R

m

R

= qui correspond à un fonctionnement optimal.

Bilan des puissances en dynamique. (régime sinusoïdal)

L’alimentation V

CC

fournit

un courant i

alim

≈ i

C

, ondulant autour de la valeur moyenne I

C0

; en conséquence,

P

alim

≈ V

CC

.I

C0

en moyenne.

Là encore, l’alimentation fournit une puissance indépendante du niveau des signaux variables :

E

2

cc

lima

R2

V

P

≈.

En sortie, la puissance reçue par R

U

est celle fournie au primaire du transformateur (supposé parfait) :La résistance

2

u

m

R

vue du primaire est soumise à l’ondulation de v

CE

(t) ; cette ondulation peut atteindre une amplitude maximale

de V

CC

/2 à pleine puissance ; on obtient ainsi :

E

2

cc

E

2

cc

2

u

2

maxce

maxu

R8

V

R

8

V

m

R

2

V

ˆ

P===

RU

u2 u1

i1 i2

C1

C1

u

E

u

S

V

CC

m

RE

0V

RU

vCE

iC

Vcc/2

0

E

cc

R

V

Vcc

Dte de charge dynamique (1)

Dte de charge statique

IC0

Dte de charge dynamique (2)

Le rendement, dans cette hypothèse, atteint 25% au maximum ; ça n’est toujours pas satisfaisant.

La conclusion qui s’impose sur la classe A est la suivante :

Les étages amplificateurs sont de structure simple et apportent très peu de distorsion ; par contre, leur rendement

médiocre provient essentiellement de leur forte dissipation thermique .

2 . Amplification de puissance en classe B.

En classe B, un transistor est polarisé avec un courant collecteur nul au repos.

Pour qu’il en soit ainsi, on polarise ce transistor à V

BE0

= 0.

Si on superpose un signal v

be

(t) alternatif, seule l’alternance

positive est susceptible de débloquer le transistor et d’être traitée

en amplification.

En conséquence, un amplificateur de signaux alternatifs en classe B

doit comporter 2 transistors complémentaires (NPN + PNP),

chacun d’entre eux se chargeant d’une alternance des signaux.

Energétiquement parlant, un étage classe B semble plus intéressant

qu’un étage en classe A, car la dissipation au repos est nulle.

Au rang des inconvénients, il faut 2 transistors complémentaires,

ainsi qu’une alimentation symétrique.

En fonctionnement, l’attaque peut s’effectuer sur les bases des

2 transistors par liaison directe ; il en est de même pour la liaison

avec la charge R

U

; ceci va rendre apte l’étage push-pull au

traitement des signaux continus ou lentement variables.

Action d’une tension de commande alternative u

E

(t).

En négligeant le seuil de conduction des transistors, nous

aurons :

- si u

E

> 0 : T

1

conduit, T

2

est bloqué et u

S

(t) ≈ u

E

(t).

- si u

E

< 0 : T

2

conduit, T

1

est bloqué et u

S

(t) ≈ u

E

(t).

Ce type d’étage n’amplifie donc pas en tension.

Par contre, le courant d’entrée pouvant s’identifier à un courant

de base et le courant de sortie à un courant de collecteur, on

peut aisément prévoir une forte amplification en courant.

(Souvent T

1

et T

2

sont des configurations Darlington)

En réalité, le seuil de conduction des transistors interdit

tout déblocage de l’un d’eux si – 0,6V < u

E

< + 0,6V.

Il en résulte une distorsion de raccordement de u

S

,

sensible à faible niveau, ainsi qu’une perte d’amplitude

de 0,6V environ. (voir ci-dessous)

Ru

Vcc

Vcc

T1

T2

Etage push-pull de

principe

au repos

0

0

0

RU

Vcc

T1

Transistor NPN polarisé

en classe B

0

0

Ru

Vcc

Vcc

T1

T2

u

E

uS

iS iE

Etage push-pull :

fonctionnement

0s 0.5ms 1.0ms 1.5ms

V(in)

V(out)

0V

-3.5V

3.5V

uE

uS

Distorsion de raccordement en classe B

Étude énergétique de l’étage push-pull, en régime sinusoïdal.

Afin de simplifier le calcul, nous idéalisons les transistors : Seuil de conduction nul et tension collecteur-émetteur

nulle en régime de saturation.

Dans ces conditions, u

E

(t) = u

S

(t) ; nous exprimerons toutes les puissances en fonction de la tension de sortie

efficace U

S

.

Puissance de sortie Trivialement :

u

2

S

u

R

U

P=

Puissance fournie par les alimentations

Chaque alimentation fournit le courant de sortie

pendant une alternance de u

E

(Cf. ci-contre)

Chaque alimentation fournit la même puissance

moyenne :

P

alim

= P

alim1

+ P

alim2

= 2P

alim1

soit

π

==

S

cc1limacclima

I

ˆ

V2i.V2P

et comme

u

S

u

S

S

R

U

2

R

U

ˆ

I

ˆ==

,

u

S

cc

u

S

cclima

R

U

V9,0

R

U

V

22

P≈

π

=

Puissance dissipée par les transistors.

C’est évidemment la différence P

alim

– P

u

; chaque transistor dissipe la même puissance moyenne (fonctionnement

complémentaire sur 50% du temps).

P

T

= P

T1

+ P

T2

= 2P

T1

= P

alim

- P

u

soit

−

π

== 2

UV2

.

R

U

PP

Scc

u

S

2T1T

P

T1

(ou P

T2

) est une fonction parabolique de

U

S

; sa dérivée

u

S

u

cc

S

1T

R

U

R

V2

dU

dP −

π

=

s’annule en

ccS

V

2

Uπ

= ≈ 0,45VCC

La puissance PT dissipée par les transistors

y passe par un maximum

u

2

2

cc

maxT

R

V2

Pπ

=.

Ci-contre, on a tracé les évolutions de ces

puissances avec US, pour VCC = 15V et RU = 8

Ω

Rendement

cc

s

lima

u

V

U

.

22

P

Pπ

==η

Le rendement d’un étage classe B augmente

proportionnellement au niveau de sortie :

A pleine puissance ( 2

V

U

cc

maxs

=) , le rendement théorique peut atteindre /4 ≈ 0,785

(Rem : Au point où PT est maximale (US ≈ 0,45VCC) , PT = PU = P

alim

/2 et le rendement est de 50% !)

0s 0.5ms 1.0ms 1.5ms

I(V2)* V(V2:-)

0W

500mW

-I(V1)* V(V1:+)

-100mW

500mW

SEL>>

P

alim1

(W)

P

alim2

(W)

Pu

Palim

Pt

Evolution des puissances dans un étage classe B

6

6

7

7

1

/

7

100%