D. Révision finale.key

Révision finale

GIF-1001 Ordinateurs: Structure et Applications, Hiver 2016

Jean-François Lalonde

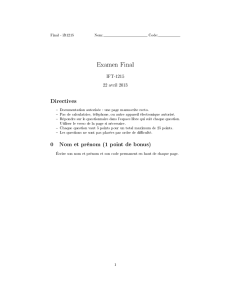

Logistique — examen final

•40% de la note totale

•Mardi 26 avril de 14h30 à 16h30

•Nous diviserons le groupe en deux:

•Andande à Gaudy: PLT-2341

•Gauvin à Weber-Boisvert: PLT-2751

•Une feuille 8.5 x 11, recto-verso, écrite à la main

Interruptions

1. Restaurer le contexte

2. Reprendre là ou le processeur était rendu

1. Terminer l’instruction en cours

2. Déterminer s’il faut traiter l’interruption.

3. Sauvegarder le contexte

4. Déterminer l’adresse de la routine de traitement de l’interruption

5. Exécuter cette routine

Interruption!

Traitement de l’interruption…

Interruptions et système d’exploitation

•2 utilités principales:

•accès aux périphériques

•exécution de plusieurs processus

Démarrer un ordinateur (“bootstrapping”)

Bootstrap loader

(dans le BIOS)

Disque dur

RAM

1. Exécution du “bootstrap

loader”, qui est stocké dans

une ROM

2. Le bootstrap “trouve”

l’emplacement du système

d’exploitation sur le disque dur!

(habituellement toujours au

même endroit)

3. Le bootstrap copie le

programme de chargement

(“loader”) du SE en RAM

4. Branchement vers la RAM pour

que le “loader” du SE puisse

s’exécuter

5. Le “loader” du SE copie

ensuite le SE en RAM

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

1

/

19

100%