Cours

Architecture des ordinateurs

15 juillet 2002

2

Table des matières

1 Introduction à l’architecture 7

1.1 Qu’appelle t-on architecture des ordinateurs? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.2 Versl’ordinateur ............................................. 7

1.2.1 Lesinventions .......................................... 7

1.2.2 Lesthéories............................................ 8

1.3 Naissancedel’ordinateur......................................... 8

1.4 Chronologie................................................ 8

1.5 Structure générale d’un ordinateur mono-processeur actuel . . . . . . . . . . . . . . . . . . . . . . . 9

1.6 Langage.................................................. 10

2 Codage des informations 13

2.1 Numération en base b........................................... 13

2.1.1 Représentation .......................................... 13

2.1.2 Opérationsarithmétiques..................................... 13

2.1.3 Conversion ............................................ 14

2.2 Représentationdesentiers ........................................ 15

2.2.1 Codagemachine ......................................... 15

2.2.2 Complémentdécimal....................................... 16

2.2.3 Complément binaire et codage des entiers négatifs . . . . . . . . . . . . . . . . . . . . . . . 16

2.3 Représentation des nombres fractionnaires . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.3.1 Changementdebase ....................................... 17

2.3.2 Virguleflottante ......................................... 18

2.3.3 Opérations sur les nombres à virgule flottante . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.3.4 Problèmed’arrondis ....................................... 18

2.4 Représentationdescaractères....................................... 19

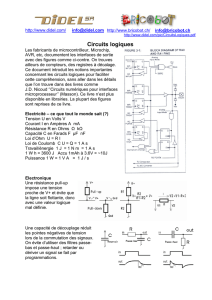

3 Algèbre de Boole et circuits logiques 21

3.1 Introduction à la logique des propositions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2 AlgèbredeBoole............................................. 21

3.3 Portesetcircuitslogiques......................................... 23

3.4 Circuitscombinatoires .......................................... 24

3.4.1 Additionneur........................................... 24

3.4.2 Incrémenteur........................................... 25

3.4.3 Comparateur ........................................... 25

3.4.4 UAL ............................................... 28

3.5 Bascules des circuits séquentiels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.5.1 Définitions ............................................ 28

3.5.2 BasculeRS............................................ 29

3.5.3 BasculeRSC ........................................... 30

3.5.4 BasculeD............................................. 31

3.5.5 BasculesJKetT ......................................... 31

3.6 Applicationdesbascules ......................................... 32

3

4TABLE DES MATIÈRES

3.6.1 Registresàdécalage ....................................... 32

3.6.2 Compteurbinaire......................................... 32

3.6.3 Mémoirederegistres....................................... 33

4 Mémoires 35

4.1 Hiérarchiedemémoire .......................................... 35

4.2 Organisationdesinformations ...................................... 36

4.2.1 Format .............................................. 36

4.2.2 Caractéristiques des mémoires . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4.2.3 Typesd’accès........................................... 36

4.3 Mémoirescaches ............................................. 36

4.3.1 Principesgénéraux........................................ 36

4.3.2 Moded’accèsdescaches..................................... 37

4.3.3 Remplacement des données dans le cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3.4 Interaction avec la mémoire centrale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.4 Mémoirecentrale............................................. 39

5 Le langage de la machine 41

5.1 Instructionsmachine ........................................... 41

5.1.1 Leprocesseur........................................... 41

5.1.2 Typesd’instructions ....................................... 41

5.1.3 Formatd’instruction ....................................... 42

5.1.4 Modesd’adressage........................................ 43

5.2 Appeldefonctions ............................................ 43

5.3 Exemples d’assembleur (montrés sur transparents) . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.4 Du programme C vers le processus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

6 Pipeline 49

6.1 Étagesd’unpipeline ........................................... 49

6.2 Registresdepipeline ........................................... 50

6.3 Performancesd’unpipeline........................................ 50

6.4 Problèmesliésaupipeline ........................................ 50

7 Unités d’un microprocesseur 53

7.1 Unitésinternes .............................................. 53

7.2 Unitédedécodage............................................. 54

7.3 MMU (Memory Management Unit) ................................... 55

7.4 Accroîtrelesperformances........................................ 55

7.5 Exemplesd’architecture ......................................... 56

7.5.1 Architecture R10.000 (MIPS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

7.5.2 LepentiumIII(Intel)....................................... 57

7.5.3 L’Athlon(AMD)......................................... 58

Table des figures

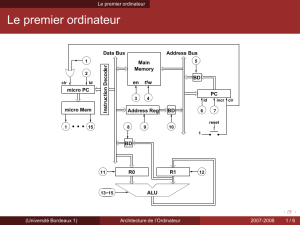

1.1 Schéma de la machine de VON NEUMANN. ............................... 9

1.2 Structure générale d’un ordinateur mono-processeur actuel. . . . . . . . . . . . . . . . . . . . . . . . 9

1.3 Évolution des processeurs Intel. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.4 Architecture d’une machine multi-niveaux. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.5 Les couches de la plupart des ordinateurs actuels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 Tables d’addition et de multiplication en base 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.2 Représentation des réels et problèmes d’arrondis. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1 Table de vérité d’une fonction et calcul de son expression booléenne. . . . . . . . . . . . . . . . . . . 23

3.2 Porteslogiquesélémentaires........................................ 23

3.3 Exempledecircuitlogique......................................... 24

3.4 Deux réalisations du demi-additionneur. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.5 Additionneur complet : table de vérité, schéma détaillé et schéma synthétique. . . . . . . . . . . . . . 25

3.6 Incrémenteur4bits............................................. 25

3.7 Comparateur. ............................................... 26

3.8 Comparateur quatre bits fabriqué à partir de comparateurs un bit (boîtes noires). . . . . . . . . . . . . 26

3.9 Indicateurdezéro. ............................................ 26

3.10Additionneur4bits............................................. 27

3.11 Représentation schématique de l’additionneur 4 bits. . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.12 Représentation schématique d’une UAL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.13 Circuit combinatoire d’une UAL rudimentaire à 1 bit possédant 4 opérations. . . . . . . . . . . . . . 29

3.14 Bascule RS : circuit logique et schéma synthétique. . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.15 Table de Karnaugh pour la bascule RS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.16 Bascule RSC : circuit logique et schéma synthétique. . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.17 Circuit logique de la bascule D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.18BasculeJK................................................. 31

3.19 Table de Karnaugh pour la bascule JK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.20 Table de vérité de la bascule JK (C=1).................................. 32

3.21BasculeT. ................................................ 32

3.22TabledevéritédelabasculeT....................................... 32

3.23 Registres à décalage à droite et illustration de leur comportement. . . . . . . . . . . . . . . . . . . . 32

3.24 Schéma d’un compteur trois bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.25 Schéma logique d’une mémoire 4×3bits................................. 34

4.1 Cacheassociatif. ............................................. 37

4.2 Cachedirect. ............................................... 37

4.3 Cache associatif par nensembles. .................................... 38

5.1 Modes d’adressage dans l’architecture VAX. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.2 Avant l’appel à somme(2). ........................................ 44

5.3 Avant l’appel à somme(1). ........................................ 44

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

1

/

58

100%