Unité centrale de traitement

1

©Pierre Marchand, 2001 280

Objectifs :

À la fin de cette unité, vous connaîtrez le fonctionnement de l'unité

centrale de traitement d'un ordinateur.

Pour y arriver, vous devrez atteindre les objectifs suivants :

- décrire les différentes composantes d'une unité centrale de

traitement et leur rôle : unité de commande, séquenceur, unité

arithmétique et logique, compteur ordinal, registre d’instruction,

horloge;

- décrire la structure d'une instruction de niveau machine;

Unité 9: Unité centrale de traitement

©Pierre Marchand, 2001 281

8.1 Architecture

L’unité centrale de traitement (UCT) ou processeur central (CPU) est

l’élément moteur de l’ordinateur qui interprète et exécute les

instructions du programme situées en mémoire centrale.

L’ensemble CPU + mémoire centrale constitue l’Unité Centrale.

L’UCT est composé de l’Unité arithmétique et logique (UAL) et de

l’Unité de commande ou de contrôle.

L’UAL effectue les opérations arithmétiques et logiques.

L’Unité de commande dirige le fonctionnement de toutes les autres

unités : UAL, mémoire, entrées / sorties, etc., en leur fournissant les

signaux de cadence et de commande.

Unité 9: Unité centrale de traitement

2

©Pierre Marchand, 2001 282

8.1 Architecture

Les différentes unités sont interconnectées par des systèmes de

câblage transportant des signaux électriques. Pour éviter de relier

chaque unité à chacune des autres, on fait usage de lignes exploitées

en commun. On appelle bus ces ensembles de lignes.

On peut distinguer trois bus différents :

• Bus d’adresses, par exemple, A0 à A31

• Bus de données, par exemple, D0 à D31

• Bus de contrôle, par exemple, R/W,

Un bus peut être utilisé par toutes les unités qui y sont connectées,

mais jamais par plus de deux unités en même temps. Ceci pose des

problèmes d’attente et d’arbitrage (contention) lors des requêtes

d’utilisation.

Unité 9: Unité centrale de traitement

©Pierre Marchand, 2001 283

8.1 Architecture

Unité 9: Unité centrale de traitement

Bus de cache Bus local Bus mémoire

CPU

Cache

niveau 2 Pont

PCI Mémoire

centrale

Bus PCI

Disque

IDE

Adaptateur

graphique

Moni-

teur

SCSI USB

Souris Cla-

vier

Modem Carte

de son Impri-

mante

Bus ISA

Pont

ISA

3

©Pierre Marchand, 2001 284

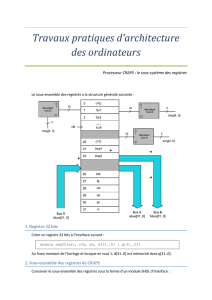

8.2 Unité de commande

Cette unité comporte

• Le compteur ordinal CO

• Le registre d’instruction RI

• Le décodeur de code opération

• Le séquenceur

• L’horloge

RA = registre d ’adresses

RM = registre mot

Unité 9: Unité centrale de traitement

Mémoire

Bus de

données

Bus

d’adresses

RMRA

CO

Horloge Séquenceur

RI

Décodeur

R/W

©Pierre Marchand, 2001 285

8.2 Unité de commande

Les impulsions générés par l’horloge à intervalles réguliers détermi-

nent le temps de cycle de la machine.

L’exécution d’une instruction prend généralement plus d’un cycle, car

une instruction comporte généralement :

• le temps de chargement de l’instruction (fetch),

• le temps de décodage de l’instruction,

• le temps de chargement des opérandes et de calcul de leur

adresse effective,

• le temps d’exécution proprement dit.

• le temps d’écriture du résultat (writeback).

En utilisant un pipeline, il est quand même possible d’émettre une

instruction par cycle si toutes ces opérations peuvent être effectuées

en parallèle.

Unité 9: Unité centrale de traitement

4

©Pierre Marchand, 2001 286

8.2 Unité de commande

Étapes d’un cycle de recherche d’instruction (fetch) :

• Transfert de l’adresse de la nouvelle instruction de CO à RA.

La génération d’une impulsion de lecture par l’unité de commande

provoque le transfert de l’instruction cherchée vers RM qui fonctionne

comme registre tampon pour tous les échanges avec la mémoire.

• Transfert de l’instruction dans RI.

Instruction = code opération + adresse opérande

L’adressage de l’opérande peut demander le calcul de l’adresse

effective, ce qui consomme des cycles machine.

Pendant que l’adresse de l’opérande est envoyée à RA, le code

opération est transmis au décodeur qui détermine le type d’opération

demandée et le transmet au séquenceur.

• Le CO est incrémenté en vue du cycle de recherche suivant.

Unité 9: Unité centrale de traitement

©Pierre Marchand, 2001 287

8.3 Synchronisation des opérations

Les signaux périodiques générés par l’horloge définissent le cycle de

base ou cycle machine (clock cycle).

Le cycle mémoire est habituellement beaucoup plus long que le cycle

machine, surtout s’il doit accéder à la mémoire centrale (échec du

cache interne L1 + échec du cache externe L2)

Par exemple, dans un processeur dit à 500 MHz, le cycle machine est

de 2 ns.

La fréquence du bus PCI pouvant atteindre 133 MHz, le cycle de bus a

une durée de 7,5 ns. Ceci est donc le temps minimum pour un accès

en mémoire centrale.

Toutefois, il faut habituellement plusieurs mots mémoire pour remplir

une rangée de cache, de sorte qu’un accès en mémoire centrale

représente plusieurs cycles de bus.

Unité 9: Unité centrale de traitement

5

©Pierre Marchand, 2001 288

8.4 Séquenceur

Le séquenceur est un automate qui a la responsabilité de générer les

signaux de commande nécessaires pour actionner et contrôler les

unités participant à l’exécution d’une instruction donnée.

Cette fonction peut être réalisée de deux façons : séquenceur câblé ou

séquenceur microprogrammé.

Un séquenceur câblé est un circuit séquentiel complexe qui fait corres-

pondre à chaque instruction un sous-circuit capable de commander son

déroulement.

On peut obtenir le même résultat avec une suite de micro-instructions

stockées dans une mémoire de microprogrammation. Ce micro-

programme est capable de générer une suite de signaux de commande

équivalent à celle qui serait produite par un séquenceur câblé.

Unité 9: Unité centrale de traitement

©Pierre Marchand, 2001 289

8.4 Séquenceur

Unité 9: Unité centrale de traitement

RI

code op adresse

décodeur

séquenceur

câblé

UAL

mémoire de

microprogrammation

commandes commandes

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

1

/

16

100%