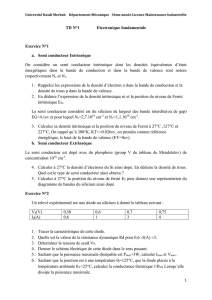

TP de Physique des Composants

Département Micro-électronique et

télécommunications

Deuxième année – 2003/2004

TP de Physique des Composants

Sandrine BERNARDINI

Pascal MASSON

Bruno IMBERT

Ecole Polytechnique Universitaire de Marseille

Laboratoire Matériaux et Micro-électronique de Provence (L2MP)

2

3

Table des matières

Valeurs des constantes .......................................................................................... 5

TP NO1 : Le transistor bipolaire ........................................................................... 7

TP NO 2 : La conductance ...................................................................................... 9

TP NO 3 : Le transistor MOS ............................................................................... 19

TP NO 4 : Courants dans une jonction PN polarisée....................................... 23

TP NO 5 : La capacité MOS.................................................................................. 25

TP NO 6 : Diode en commutation de l’état passant à l’état bloqué. Charges

stockées. Temps de recouvrement inverse ......................................................... 27

TP NO 7 : Capacité d’une jonction PN polarisée en inverse ........................... 29

ANNEXE 1 : Nombre de Gummel ................................. Erreur ! Signet non défini.

ANNEXE 2 : Temps de recouvrement inverse des diodes ................................ 31

4

5

Valeurs des constantes

Les constantes à utiliser à température ambiante, T = 300 K, au cours de ces TP sont :

La charge d’un trou

q = 1.61019 C

Permittivité du vide

0 = 8.851012 Fm1

Permittivité du silicium

Si = 11.9 0

Permittivité de l’oxyde de silicium

ox = 3.9 0

Constante de Planck

h = 6.6261034 Js

Constante de Boltzmann

k = 1.3811023 JK1

Masse de l’électron

M0 = 0.9111030 Kg

Largeur de la bande interdite

EG = 1.12 eV

Concentration intrinsèque de porteurs

ni = 1.171010 cm3

Densité effective d’état dans la bande de valence

du silicium.

NV = 1.041019 cm3

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

1

/

31

100%