10. Les interruptions

1

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

Chap.10

Interruptions

MounirBoukadoum

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

Programmesetpilotesdepériphériques

2

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

Principegénérald’uneinterruption

•Arrêttemporairedel'exécutiond'un

programme,suiteàunévènement

logicieloumatériel,afind'exécuter

unsous‐programmedontl’adresse

dépenddutyped’évènement

•L’exécutiondusous‐programmese

termineparlarestaurationdel'état

sauvéduCPUquirepartdel'endroit

oùilaétéinterrompu.

•Différenceavecunsousprogramme

conventionnel:

–L’adressedusautestprédéfinie

–Certainsregistressontsauvés

automatiquementlorsdusautet

remisenétatauretour

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

Exemplesd’évènementssources

d’interruptions

Déplacement desouris

Entréedecaractère auclavier

Secteur dedisque défectueux

Compte terminald’untemporisateur

Disfonctionnement del’imprimante

Accès delacartevidéo vers lamémoire

Emissionetréception parleModem

Faute d’accès en mémoire

Lectured’uncoded’instruction inconnu

Etc.

3

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

Butsd’utilisation

•Gestiondeconditionsd’exception

•Communicationnonbloquante avecdes

périphériquesexternes

–Communicationsansdélaisd’attentequimènesouventà

uneéconomied’énergieenmettantleCPUdansunétat

dormantaulieudetournerdansuneboucled’attente.

•Appelsdeserviceetcommutationdetâchesdansun

systèmegéréparunprogrammed’exploitation

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

Deuxtypesfondamentaux

d’interruptions

•Logicielle

–L’instructionSWI détourneleprogrammeversunautre

programme(e.g.servicedusystèmed’exploitation)

•Matérielle

–UnsignalinterneduCPUouuneligneexternedétournele

programmeversunautreprogramme(e.g.pilotede

périphérique)

•Permetlasynchronisationsanspasserparuneboucled’attente.

•Cellesenprovenanced’unehorlogepeuventpermettrela

répartitiondestâchesdansunsystèmemultitâchesoumulti‐

usager

4

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

Branchementdesourcesmutiples

Lignes individuelles

à drain/collecteur

ouvert

Ligne de requête externe commune

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

•Lesétapesavantetaprèsl’exécutiondelaroutinederéponseà

l’interruptionintroduisentdesdélaisquis’ajoutentautempsderéponse

–Effetlimitatifsurlenombredesourcesentemps‐réel

•Lessourcesontdesprioritésfixesouprogrammables

–Blocagedesourcesdemoindreprioritépard’autresdeprioritéplusélevée

IRQ

Processusgénérald’interruption

5

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises

adresse source

d’IRQ Bit

CCR Bit

spécifique adresse source

d’IRQ bit du

CCR Bit de

gestion

0xffc0-d5 Réservés - - 0xffea-b IC3 I IC3I

0xffd6-7 SCI I RIE, TIE,

TCIE, ILIE 0xffec-d IC2 I IC2I

0xffd8-9 SPI I SPIE 0xffee-f IC1 I IC1I

0xffda-b PA I PAII 0xfff0-1 RTI I RTII

0xffdc-d PA

OFLW I PAOVI 0xfff2-3 IRQ I -

0xffde-f TIMER I TOI 0xfff4-5 XIRQ X -

0xffe0-1 IC4/OC5 I I4/O5I 0xfff6-7 SWI - -

0xffe2-3 OC4 I OC4I 0xfff8-9 Ill.

Opcode --

0xffe4-5 OC3 I OC3I 0xfffa-b COP - NOCOP

0xffe6-7 OC2 I OC2I 0xfffc-d CLK

mon. --

0xffe8-9 OC1 I OC1I 0xfffe-f RESET - -

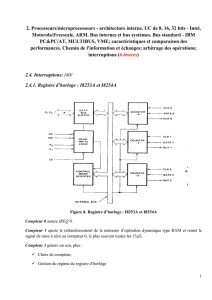

Adresses des routines

de réponse

• Appelées vecteurs

• Emmagasinées dans

une table

• Les priorité sont établies

par la position dans la

table

Ex. Vecteurs d’interruption

normaux du 68HC11 et bits

de commande associés

Traduit et adapté de l’anglaisTraduit et adapté de sources anglaises Monjy Rabemanantsoa 10

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

1

/

18

100%