Énoncé du TP en format PDF

!"#$%&'()"*+,*'")-')"(,(',&../$-&'$0%*,

12345665+,7$8(",965:,

,

,

;<=>=2?,@<=;2ABC,D!,:,

<E.0%*(,F,)%,&..(/,#(,*("8$-(,

,

G(, '"&8&$/, ."&'$H)(,8&)', IJ, #(, /&, %0'(, '0'&/(, #), -0)"*K, L, M&$"(, $%#$8$#)(//(N(%'+, $/, *("&,

-0""$OE,*)",)%,'0'&/,#(,56,.0$%'*K,?(,'"&8&$/,(*',F,"(N(''"(,&),./)*,'&"#,N("-"(#$,/(,5(",,&8"$/,F,

9IP:QK,?&,."0-E#)"(,#(,"('&"#,#E'&$//E(,#&%*,/(,./&%,#(,-0)"*,*R&../$H)(K,

,

!STCG;23U,

G(,'"&8&$/,."&'$H)(,8$*(,/(*,0VW(-'$M*,*)$8&%'*,X,

• G0N."(%#"(,-0NN(%',M0%-'$0%%(%',/(*,$%'("").'$0%*,#R)%,0"#$%&'()",

• G0N."(%#"(,-(,H)R(*',)%,&..(/,#(,*("8$-(,#),*Y*'ZN(,#R([./0$'&'$0%,

,

\D!DG\,

,

G(,'"&8&$/,."&'$H)(,(*',#$8$*E,(%,#()[,E'&.(*,."$%-$.&/(*,X,,

5K \-"$"(, )%, -0)"', -0#(, (%, &**(NV/()", =<], "(/$E, F, /R$%*'")-'$0%, U^2,.0)", )%, -_)",

=<]`;a]2,b-0NN(,.0)",/(*,;@*,."E-E#(%'*c,d,

9K aE-"$"(,/&,O(*'$0%,#(*,$%'("").'$0%*,.&",)%,-_)",=<]4G0"'([,]IK,

,

Étape&1,&code&assembleur&

>0'"(, -0#(, &**(NV/()", #0$', N(''"(, /(, %)NE"0, #R)%, &..(/, #(, *("8$-(, #&%*, /(, "(O$*'"(, <6+,

/0"*H)R)%, &..(/, #(, *("8$-(, *(, ."0#)$'K, ?(*, &..(/*, #(, *("8$-(, *0%', OE%E"E*, .&", /(*,

&../$-&'$0%*,#(,/R)*&O("+,/0"*H)(,-(*,&../$-&'$0%*,)'$/$*(%',/R$%*'")-'$0%,U^2,efK,?R$%*'")-'$0%,

U^2, #E-/(%-P(, )%(, $%'("").'$0%, /0O$-$(//(K, >0)*, #(8(g, $N./EN(%'(",/&, "0)'$%(, '"&$'&%',

/R$%'("").'$0%,.0)",H)(,<6,*0$',N$*,EO&/,F,f,b<6,h,fc,/0"*H)(,/R$%'("").'$0%,*(,."0#)$'K,a(,

./)*+, 80)*, #(8"(g, E-"$"(, /&, V0%%(, (%'"E(, #&%*, /&, '&V/(, #(*, 8(-'()"*, #R$%'("").'$0%, #),

*Y*'ZN(,.0)",H)(,/(*,$%'("").'$0%*,*0$(%','"&$'E(*K,,

,

]&$%,

U0)*4<0)'$%(,'"&$'&%',/R$%'("").'$0%,/0O$-$(//(,U^2,

N&$%X,

,,U^2,,e6[5599II,

,,U^2,e6[ii::jj,

,,S,N&$%,

]0%2U<.0)"2%'?0O$-$(//(,X,

,,d>0'"(,-0#(,$-$,.0)",N(''"(,<6,h,6[5599II,0),6[ii::jj,

,,d>0'"(,-0#(,$-$,.0)",N(''"(,<6,h,6[5599II,0),6[ii::jj,

,,d>0'"(,-0#(,$-$,.0)",N(''"(,<6,h,6[5599II,0),6[ii::jj,

,,da0$',"('0)"%(",&),N&$%k,

,,

Étape&2,&description&de&la&gestion&des&interruptions&par&ARM9Cortex&M3&

@0)", #E-"$"(, -0NN(%', )%, N$-"0."0-(**()", =<]4G0"'([, ]I, OZ"(, /(*, $%'("").'$0%*+,

"&..(/(g480)*, H)(, /0"*, #R)%(, $%'("").'$0%+, /(*, N$-"0."0-(**()"*+, #(, N&%$Z"(, OE%E"&/(+,

(MM(-')(%',/(*,0.E"&'$0%*,*)$8&%'(*,X,

,

• ;("N$%(,/(,0),/(*,$%*'")-'$0%*,(%,-0)"*,

• >E"$M$(,*$,/R$%'("").'$0%,.()',l'"(,'"&$'E(,b."$0"$'E,(',N&*H)(c,

!"#$%&'()"*+,*'")-')"(,(',&../$-&'$0%*,

12345665+,7$8(",965:,

,

,

• U&)8(O&"#(,/(,-0%'(['(,(%,-0)"*,

• !V'$(%',/R&#"(**(,#(,/&,"0)'$%(,*("8&%',F,'"&$'(",/R$%'("").'$0%,b2U<c,

• CMM(-')(,)%,*&)',F,/R&#"(**(,#(,/R2U<,

>0)*,#(8(g,#E-"$"(,/&,M&m0%,#0%',-P&-)%(,#(,-(*,E'&.(*,*0%',([E-)'E(*,#&%*,/(,-_)",=<]4

G0"'([, ]IK,L, '$'"(, #R([(N./(+, 80)*, "('"0)8("(g, /&, "E.0%*(, H)R$/, M&)#"&$', #0%%(", .0)", /(,

-_)",=<]`;a]2,-$4#(**0)*,X,-R(*',/(,-_)",)'$/$*E,.&",#EM&)',#&%*,/(*,'"&8&)[,."&'$H)(*,(',

-R(*', -(/)$, .0)", /(H)(/, 80)*, #(8(g, E-"$"(, /(, -0#(, -$4#(**)*K,Indice,X, /(, #0-)N(%',

n,=<]`;a]2K.#M,o+,#$*.0%$V/(,*)",/(,*$'(,p(V,#),-0)"*+,&,E'E,)'$/$*E,.0)",#E-"$"(,/(*,E'&.(*,

-$4V&*k,'"0)8(g,/REH)$8&/(%',.0)",/(,=<]4G0"'([,]Iq,

,

;7\!<2C,

,

!"#$%&'($)*"#"+),--$.)/$)%$012($)345678)

?R$%*'")-'$0%, U^2, 0), U>G, bNlN(, -P0*(, H)(, U^2+, N&$*, .0)", /(*, N$-"0."0-(**()"*, ./)*,

"E-(%'*c,(*',)'$/$*E(, .0)", .("N(''"(,&),."0O"&NN()", #R&..(/(",#(*, M0%-'$0%*, #), *Y*'ZN(,

#R([./0$'&'$0%K,

,

7&V$')(//(N(%'+, /(, ."0O"&NN()", %(, *&$', .&*, /(, %0N, #(*, M0%-'$0%*, 0), /(*, &#"(**(*, #(*,

M0%-'$0%*, #), *Y*'ZN(, #R([./0$'&'$0%, .0)", ([E-)'(", #(*, 'r-P(*, #), !UK, @&", ([(N./(+, /(,

."0O"&NN()",%(,*&$',.&*,/R&#"(**(,#(,/&,M0%-'$0%,.("N(''&%',#(,/&%-(",)%,'P"(&#,0),#(,-(//(,

.("N(''&%',#R&MM$-P(",H)(/H)(,-P0*(,F,/RE-"&%K,C%,M&$'+,/(,."0O"&NN()",%(,8()',.&*,*&80$",/(*,

&#"(**(*,#(,'0)'(*,/(*,M0%-'$0%*,#),!Uk,,

,

B%(,M&m0%,M&-$/(,#R&..(/(",#(*,*0)*4"0)'$%(*,*&%*,-0%%&s'"(,/()"*,&#"(**(*,(*',#R)'$/$*(",)%(,

$%'("").'$0%,X, /(, *Y*'ZN(, #R([./0$'&'$0%, "(N./$', /&, '&V/(, #(*, 8(-'()"*, #R$%'("").'$0%, .0)",

H)(,/(*,."0O"&NN()"*,&..(//(%',/(*,M0%-'$0%*,80)/)(*,/0"*H)R$/*,/&%-(%',#(*,$%'("").'$0%*,

/0O$-$(//(*K,

,

?R$%*'")-'$0%, U^2, ef, /&%-(, )%(, $%'("").'$0%, /0O$-$(//(K, ?0"*, #), '"&$'(N(%', #(, -(''(,

$%'("").'$0%+, /(, *Y*'ZN(,#R([./0$'&'$0%,"E-).Z"(,/&,8&/()",#(,f,(', &--0N./$',)%(, 'r-P(,(%,

M0%-'$0%,#(,-(//(4-$K,

,

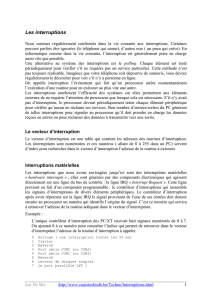

9:;;$+&)0<("-<0$0)=)/$)456)>=8)

?0"*, #(, /R$%'("").'$0%, /0O$-$(//(+, /(, "(O$*'"(, ?<, -0%'$(%', /R&#"(**(, #(, "('0)"K, @)$*H)(,

/R$%*'")-'$0%,&8&%',-(//(,F,/R&#"(**(,#(,"('0)",(*',M0"-EN(%',U^2,ef+,$/,(*',.0**$V/(,#(,/$"(,/(*,

0-'('*,-0%*'$')&%',-(''(,$%*'")-'$0%K,2/,(*',#0%-,.0**$V/(,#R(['"&$"(,efk,

,

?&,8&/()",#(, f, (*', *)",9iV$'*+,/R0.-0#(,#(,U^2,b6[(Mc,E'&%',*)",t, V$'*K,@0)",(['"&$"(,f, #(,

/R$%*'")-'$0%, $/, M&)', N&*H)(", /R0.-0#(,&M$%, #(, -0%*("8(", /(*, 9i, V$'*, /(*, N0$%*, *$O%$M$-&'$M*K,

u]&*H)("u, *$O%$M$(, )'$/$*(", /R$%*'")-'$0%, =Da, &8(-, /(*, V$'*, H)(, %0)*, 80)/0%*, -0%*("8(", , F,

n,5,oK,@&",([(N./(+,*$,80)*,80)/(g,O&"#(",/(*,H)&'"(,V$'*,/(*,N0$%*,*$O%$M$-&'$0%,#(,<6+,80)*,

!"#$%&'()"*+,*'")-')"(,(',&../$-&'$0%*,

12345665+,7$8(",965:,

,

,

M&$'(*,=Da,<6+,<6+,e6[63K,U$,<6,8&/&$',6[59Ii:j`t,&8&%',/R([E-)'$0%,#(,=Da,<6+,<6+,e6[63+,

<6,8&)#"&,6[6666666t,&."Z*,/R([E-)'$0%K,,

)

9:;;$+&).$)(?"0)@ABCDBE6)FG0$'&'2.).$%)2+&$00"-&2:+%8)

?0"*,#R)%(, $%'("").'$0%+, /(*, N$-"0."0-(**()"*+, #(, N&%$Z"(, OE%E"&/(+, (MM(-')(%',/(*,

0.E"&'$0%*,*)$8&%'(*,X,

,

• ;("N$%(,/(,0),/(*,$%*'")-'$0%*,(%,-0)"*,

• >E"$M$(,*$,/R$%'("").'$0%,.()',l'"(,'"&$'E(,b."$0"$'E,(',N&*H)(c,

• U&)8(O&"#(,/(,-0%'(['(,(%,-0)"*,

• !V'$(%',/R&#"(**(,#(,/&,"0)'$%(,*("8&%',F,'"&$'(",/R$%'("").'$0%,b2U<c,

• CMM(-')(,)%,*&)',F,/R&#"(**(,#(,/R2U<,

,

;0)'(M0$*+, -(*, 0.E"&'$0%*, %(, *0%', .&*, (MM(-')E(*, #(, /&, NlN(, N&%$Z"(, .&", '0)*, /(*,

N$-"0."0-(**()"*K,@0)",/(,=<]`;a]2+,/(*,&-'$0%*,*)$8&%'(*,*0%',(MM(-')E(*,X,

,

• ;("N$%(,/(,0),/(*,$%*'")-'$0%*,(%,-0)"*,

• ?(, =<]`;a]2, &, )%, .$.(/$%(, #(, I, E'&O(*,X, 3('-P+, aE-0#(+, C[E-)'(K, U()/(,

/R$%*'")-'$0%, F, /RE'&.(, C[E-)'(, (*', '("N$%E(, /0"*H)(, /R$%'("").'$0%, *)"8$(%'K,

?(*,&)'"(*,$%*'")-'$0%*,*0%',&%%)/E(*K,

• ?(*,$%*'")-'$0%*,./)*,/0%O)(*,#),-_)",b?a],(',U;]c,*0%',$%'(""0N.)(*,(%,

./($%,N$/$(),.0)",&**)"(",)%,'(N.*, -0)"',#R(%'"E(,#&%*,/R$%'("").'$0%K,a(*,

#"&.(&)[, *.E-$&)[, #), -_)", .("N(''(%', #(, "(."(%#"(, /R([E-)'$0%, #(, -(*,

$%*'")-'$0%*,&."Z*,/v$%'("").'$0%K,

• >E"$M$(,*$,/R$%'("").'$0%,.()',l'"(,'"&$'E(,b."$0"$'E,(',N&*H)(c,

• ?&, ."$0"$'E, #(*, $%'("").'$0%*, #), -_)", =<]`;a]2, (*', /&, *)$8&%'(,b#), ./)*,

."$0"$'&$"(,&),N0$%*,."$0"$'&$"(cX,<(*('+,a&'&,=V0"'+,32A+,2<A+,@"(M('-P,=V0"'+,

B%#(M$%(#,$%*'")-'$0%,(',U^2K,,

• U&)8(O&"#(,/(,-0%'(['(,(%,-0)"*,

• ?(, N$-"0."0-(**()", =<]`;a]2, )'$/$*(, #(*, V&%H)(*, #(, "(O$*'"(*, .0)",

*&)8(O&"#(",/(,-0%'(['(,#),."0O"&NN(,$%'(""0N.)K,2/,Y,&,)%,"(O$*'"(,?<+,)%,

"(O$*'"(, U@, (', "(O$*'"(, #(, #"&.(&)[, bU@U<c, .&", -0%'(['(, .0**$V/(, b)%(,

V&%H)(,#(,"(O$*'"(*c,.0)",M&$"(,/(,/$(%,&8(-,/(*,&#"(**(*,#(,"('0)",(',&80$",

)%(,.$/(,.&",-0%'(['(K,

o ?0"*,#R)%(,$%'("").'$0%,U^2wU>G,.&",([(N./(+,/(,"(O$*'"(,?<,)'$/$*E,

*("&,?<x*8-K,?&,8&/()",N$*(,&)'0N&'$H)(N(%',#&%*,-(,"(O$*'"(,.&",/(,

N$-"0."0-(**()", *("&,/R&#"(**(, #(, "('0)", #(, /R2U<, /0"*H)(,

/R$%'("").'$0%,U^2wU^G,*("&,'("N$%E(K,

o ?(*,&)'"(*,"(O$*'"(*,#),-0%'(['(,#0$8(%',l'"(,*&)8(O&"#E(*,*)",/&,.$/(,

#(,/R$%'("").'$0%,(',"(N$*,F,/()",8&/()",$%$'$&/(,F,/&,M$%,#(,/R2U<K,

• !V'$(%',/R&#"(**(,#(,/&,"0)'$%(,*("8&%',F,'"&$'(",/R$%'("").'$0%,b2U<c,

!"#$%&'()"*+,*'")-')"(,(',&../$-&'$0%*,

12345665+,7$8(",965:,

,

,

• ?&,'&V/(,#(*,8(-'()"*,#R$%'("").'$0%,#),=<]`;a]2,-0%'$(%',t,8&/()"*,#(,I9,

V$'*+, -P&H)(, 8&/()", E'&%', /R$%*'")-'$0%, F, ([E-)'(", /0"*H)(, /R$%'("").'$0%,

*)"8$(%'+, ./)'y', H)(, /R&#"(**(, #(, /&, "0)'$%(, #(, /R$%'("").'$0%, F, '"&$'(", b)%(,

8"&$(,'&V/(,#(,8(-'()"*,#R$%'("").'$0%,-0%'$(%',#(*,&#"(**(*,./)'y',H)(,#(*,

$%*'")-'$0%*qcK,

• ?&,'&V/(,#(*,8(-'()"*,#R$%'("").'$0%,(*',F,/R&#"(**(,6,(',-0%'$(%',/(*,8(-'()"*,

*)$8&%'*,X,

,

=#"(**(,

n,>(-'()",o,#R$%'("").'$0%,

6[66666666,

<(*(',

6[6666666i,

B%#(M$%(#,2%*'")-'$0%,

6[6666666t,

U^2,0),U>G,

6[6666666G,

@"(M('-P,=V0"',

6[66666656,

a&'&,=V0"',

6[6666665i,

<(*("8(#,,

6[6666665t,

2<A,

6[6666665G,

32A,

,,

• CMM(-')(,)%,*&)',F,/R&#"(**(,#(,/R2U<,

• ?0"*, #R)%(, $%'("").'$0%+, @G, (*', N$*, F, /R&#"(**(, #(, /&, '&V/(, #(*, 8(-'()"*,

#R$%'("").'$0%, -0""(*.0%#&%', F, /&, %&')"(, #(, /R$%'("").'$0%, *)"8(%)(K, @&",

([(N./(+, /0"*, #(, <(*('+, @G, *("&, N$*, F, 6K, ?0"*, #R)%(, 2<A, b$%'("").'$0%,

N&'E"$(//(c+,@G,#(8$(%#"&,&)'0N&'$H)(N(%',6[5tK,

o ?(*, $%*'")-'$0%*, H)R0%, "('"0)8(, #&%*, /&, '&V/(, #(*, 8(-'()"*,

#R$%'("").'$0%,*0%',P&V$')(//(N(%',#(*,$%*'")-'$0%*,#(,V"&%-P(N(%',

bSc+,*&)M,.0)",/(,32Ak,,

)

=B;<CU,Cf21CDGCU,

<(N(''(g, /(, M$-P$(", asm.s,-0%'(%&%', 80'"(, -0#(+, &8(-, /&, #(*-"$.'$0%, #(, /&, O(*'$0%, #(*,

$%'("").'$0%*,#),G0"'([4]I,(%,-0NN(%'&$"(,F,/&,M$%,#),M$-P$("K,,

,

;0)', ."0O"&NN(, *&%*, -0NN(%'&$"(*,*(, 8(""&, &''"$V)(",/&, %0'(, #(, 6K,2/, M&)', &), N0$%*, )%,

-0NN(%'&$"(,'0)'(*,/(*,'"0$*,/$O%(*,#R&**(NV/()"K,

,

;0)*,/(*,"(O$*'"(*,#0$8(%',-0%*("8(",/()"*,8&/()"*,/0"*,#R)%,&..(/,#(,M0%-'$0%,0),#(,"0)'$%(,

#(,'"&$'(N(%',#R$%'("").'$0%+,F,N0$%*,H)(,-()[4-$,%(,*0$(%',)'$/$*E*,-0NN(,.&"&NZ'"(*,#(,

*0"'$(K,=)'"(N(%',#$'+,/&,8&/()",#(*,"(O$*'"(*,#0$',l'"(,-0%*("8E(*,#&%*,/&,M0%-'$0%,b<(O$*'"(*,

h,zf{d,S?,]&30%-'$0%d,<(O$*'"(*,h,zf{,(%-0"(cK,,

,

S0%,'"&8&$/q,

,

1

/

4

100%