Architectures des microprocesseurs

T. Paquet Architectures des microprocesseurs Master I 1

Architectures des microprocesseurs

Plan

Introduction générale : architecture en couches

Partie I : Structure générale d’une architecture

1. Structure générale d’une architecture

2. Organisation générale de l’unité centrale

3. Exécution d’une instruction

4. Exécution / Interprétation

5. Principes de conception RISC

6. Parallélisme d’instructions

7. Parallélisme du processeur

8. La mémoire principale

9. Principales architectures

1. Pentium II

2. UltraSparc II

2. picoJava II

Partie II : La couche microarchitecture

1. Introduction

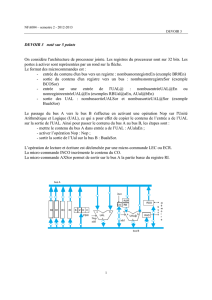

2. Exemple: Le modèle de l’IJVM

3. La micro-instruction

4. Le micro-programme

5. La micro-architecture MIC1

Partie III : La couche ISA

1. Propriétés de la couche ISA

2. Aperçu de la couche ISA du PENTIUM IV

3. Aperçu de la couche ISA de l‘Ultra SPARC III

4. La couche ISA de l’IJVM

www.univ-rouen.fr/psi/paquet/

T. Paquet Architectures des microprocesseurs Master I 2

Introduction : Architecture en couches

1. Pour maîtriser la complexité d’un ordinateur…

- L’utilisateur souhaite faire Y mais l’ordinateur ne peut faire que X

- La machine ne sait travailler qu’avec des représentations binaires et un ensemble

d’instructions réduit : langage machine L0 pour la machine M0

- Nécessité de construire un langage de plus haut niveau : L1

- Machine virtuelle M1: celle qui pourrait exécuter le langage L1

- Pour que l’exécution du programme écrit en L1 soit possible (bien que M1 n’existe pas)

il faut le traduire en L0 qui sera exécuté sur la Machine M0

Exemple:

Pour réaliser des programmes exécutables sur toutes les plateformes, le langage java est

compilé pour être exécuté sur une machine virtuelle: la JVM.

Il existe pour chaque plateforme des simulateurs de la JVM qui permettent d’exécuter un

code binaire pour la JVM.

Il existe également des processeurs qui implémentent le jeux d’instruction de la JVM

T. Paquet Architectures des microprocesseurs Master I 3

Introduction : Architecture en couches

2. Architectures actuelles en six couches

Couche logique numérique

Couche microarchitecture

Couche architecture du jeux d’instructions

Couche ISA

Couche du système d’exploitation

Couche du langage d’assemblage

Couche des langages d’application

Exécution matérielle du programme de niveau 1

Interprétation par le microprogramme

ou exécution par le matérielle

Interprétation partielle

(organisation de la mémoire, périphériques…)

Traduction (assembleur)

Traduction (compilateur)

Niveau 0

Niveau 1

Niveau 2

Niveau 3

Niveau 4

Niveau 5

Niveau programmeur

Niveau concepteur

de la machine

T. Paquet Architectures des microprocesseurs Master I 4

Partie I: Structure générale d’une

architecture

T. Paquet Architectures des microprocesseurs Master I 5

1. Structure générale d’une architecture

UAL

Unité de

commande

Registres

Unité centrale

Mémoire

Principale

Disque

Imprimante

Périphériques d’E/S

Machine de Von Neuman

- arithmétique binaire

- programme numérique rangé en mémoire

première machine : EDSAC

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

1

/

107

100%