Cas d`un inverseur TTL

Page 1 sur 15

Caractéristiques des Circuits Intégrés Numériques

Technologie TTL - Série 74 (Transistor Transistor Logic)

Ou

logique à transistor bipolaires

Dans cette série, il existe 7 grandes familles :

TTL standard 74 x x TTL low power schottky 74 L S x x

TTL low power 74 L x x TTL advanced schottky 74 A S x x

TTL schottky 74 S x x TTL advanced low power schottky 74 A L S x x

TTL fast 74 F x x

Code de désignation :

Exemple

: SN 74 LS 020 N

Pour un même numéro de type de circuit, la fonction et le brochage sont identiques.

En général, c’est la vitesse (temps de propagation interne du signal) ou la puissance

dissipée qui déterminent le choix d’une famille.

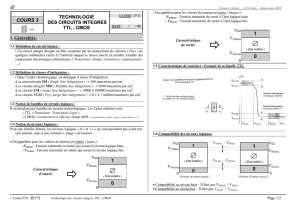

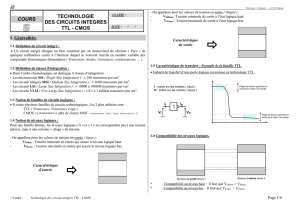

2

V

NL

V

NH

V

ILmax

V

IHmin

V

OLmax

V

OHmin

état logique 1

état logique 0

bande

indéterminé

tension

état logique 1

état logique 0

bande

indéterminé

gammes des tensions en sortie exigences des tensions en entrée

Paramètres tensions

V

IHmin

: tension d’entrée niveau haut

Niveau de tension nécessaire pour avoir un 1 logique en entrée d’un circuit

logique

Toute tension inférieure à ce niveau n’est pas considérée comme un état 1 (haut)

V

ILmax

: tension d ‘entrée niveau bas

Niveau de tension nécessaire pour avoir un 0 logique en entrée

Toute tension supérieure à ce niveau n’est pas considérée comme un état 0 (bas)

V

OHmin

: tension de sortie niveau haut

Niveau minimal de tension en sortie d’un circuit logique correspondant à l’état

logique 1

V

OLmax

: tension de sortie niveau bas

Niveau maximal de tension en sortie correspondant à l’état logique 0

Page 2 sur 15

3

Cas d'un inverseur TTL

Structure de base

Si E = Vcc transistor saturé S ≈ 0

Si E = 0 transistor bloqué S ≈ +Vcc

Caractéristique de transfert

V

CC

R

C

R

B

E

S

4

Page 3 sur 15

Sorties d’un circuit logique

Sortie normale (type totem-pôle)

Une sortie "totem-pole" est une sortie qui est capable de

fournir les niveaux 0L et 1L.

Il est interdit, sous peine de court-circuit entre alimentation

et masse, de relier ces sorties entre elles.

Toutefois, si l'on souhaite augmenter la sortance d'une

fonction, il est possible de connecter des sorties entre elles,

à condition qu'elles fournissent chacune le même signal de

sortie.

Dans le cas présenté ici, les états de sortie (0L ou 1L) sont

obtenus par mise en conduction de T2 ou T3.

Sortie collecteur ouvert

Une sortie "collecteur ouvert" n'est capable de fournir que

le niveau 0L ... et rien d'autre.

Le niveau 1L est fourni par une résistance externe dite

résistance de rappel ou de "pull-up" (de l’ordre de 1 kΩ à

10 kΩ).

Ces sorties peuvent être connectées entre elles et à une

résistance de rappel afin de réaliser des fonctions

- "ET câblé" et "OU câblé"

- d'interfaçage (passage d'un niveau logique à un autre)

- de multiplexage d'informations et des connexions à un bus

Le montage à collecteur ouvert, même en utilisant une résistance minimale, est beaucoup

plus lent que les sorties TTL en totem-pôle. Il ne faut pas utiliser ces circuits dans les

applications où la rapidité de commutation est un paramètre essentiel.

Une valeur de R faible offrira un temps de montée plus court, au détriment d'une plus

grande consommation

5

Page 4 sur 15

Sortie trois états (3-state output)

Une sortie "trois états" (three state) ou "3S" est une sortie qui est

capable de fournir

- le niveau logique "0"

- le niveau logique "1"

... et un état haute impédance qui permet la déconnexion,

l'isolement de cette sortie du reste du système (T2 et T3 bloqués)

Les sorties "trois états" sont faites pour être connectées entre elles

sans résistance de "pull-up". Elles ont des temps de montée et de

descente rapides et permettent les connexions à un bus de données

ou d'adresses..., ce qui revient à un multiplexage temporel de ces

signaux

Cas des entrées non utilisées en logique TTL :

Une entrée non connectée (en l'air) est à l'état haut.

Il est toutefois conseillé de ne pas laisser une entrée en l'air, car elle devient sensible aux

bruits.

Dans la mesure du possible, elle doit être reliée à Vcc.

On peut aussi la relier à une entrée utilisée ou à la masse, mais ceci augmente la

consommation du circuit.

Ne jamais réunir deux sorties normales ensemble, risque de court-circuit !

Seules les sorties à collecteurs ouverts

peuvent être reliées ensemble.

6

Page 5 sur 15

Paramètres courants

I

IH

: courant d’entrée niveau haut (courant entrant)

Courant qui traverse une borne d’entrée quand une tension niveau haut est appliquée

à cette entrée

I

IL

: courant d’entrée niveau bas (courant sortant)

Courant qui traverse une borne d’entrée quand une tension niveau bas est appliquée

à cette entrée

I

OH

: courant de sortie niveau haut (courant sortant)

Courant qui traverse une borne de sortie placée au niveau 1 dans des conditions de

charge spécifiées

I

OL

: courant de sortie niveau bas (courant entrant)

Courant qui traverse une borne de sortie placée au niveau 0 dans des conditions de

charge spécifiées

I

IL

I

IL

I

IL

I

OL

Etat bas

I

IH

I

IH

I

IH

I

OH

Etat haut

V

CC

R

C

R

B

E

S

7

V

NL

V

NH

V

ILmax

V

IHmin

V

OLmax

V

OHmin

état logique 1

état logique 0

bande

indéterminé

tension

état logique 1

état logique 0

bande

indéterminé

gammes des tensions en sortie exigences des tensions en entrée

Page 6 sur 15

Immunité aux bruits

L’immunité aux bruits d’un circuit logique définit l’aptitude du circuit à tolérer des

tensions parasites sur ses entrées. La mesure quantitative de l’immunité aux bruits est

appelée la marge de bruit (noise margin).

La marge de bruit à l’état haut VNH est définie comme : V

NH

= V

OHmin

- V

IHmin

La marge de bruit à l’état bas VNL est définie comme : V

NL

= V

ILmax

- V

OLmax

8

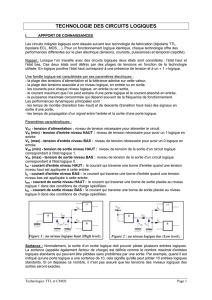

t

PHL

entrée

sortie

t

PLH

Temps de propagation (ou retards de propagation)

Un signal logique qui traverse un circuit subit toujours un retard.

Deux retards de propagation sont définis :

t

PLH

: retard pour passer du niveau BAS au niveau HAUT

t

PHL

: retard pour passer du niveau HAUT au niveau BAS

Les retards sont mesurés entre les points à mi-hauteur des transitions d’entrée et de sortie.

Exemple d’un inverseur :

Généralement, t

PHL

et t

PLH

sont différents et varient tous les deux selon les conditions de

charge.

Ces temps de propagation servent généralement de mesure pour la vitesse relative des

circuits logiques.

Consommation

Tous les CI en fonctionnement consomment une certaine quantité d’énergie électrique.

Cette énergie est délivrée par une ou plusieurs tensions d’alimentation raccordées aux

broches d’alimentation du boîtier. Généralement il n’y a qu’une borne d’alimentation par

boîtier, appelé V

CC

(pour les TTL) ou V

DD

(pour les MOS).

Si I

CC

est le courant absorbé par le CI, alors la puissance réelle consommée P

D

est le

produit I

CC

x V

CC

.

En général, I

CC

varie selon les états du circuit.

On définit I

CCH

lorsque toutes les sorties sont à 1, et I

CCL

lorsque toutes les sorties sont à 0.

Alors I

CCmoy

=

2

II

CCLCCH

+

ET P

Dmoy

= I

CCmoy

x V

CC

9

Page 7 sur 15

Sortance, Entrance

Normalement, la sortie d’un circuit logique doit piloter plusieurs entrées logiques.

Lors des associations de circuits, la somme des courants d’entrée ne doit pas être

supérieure au courant de sortie du circuit qui les commande.

La sortance (fan out) est le nombre maximal d’entrées que l’on peut connecter à une

sortie.

Elle s’exprime en Unité de charge Logique (U.L.).

La définition d’une charge unitaire est la suivante : 40 µ

µµ

µA à l’état HAUT et 1,6 mA à

l’état BAS.

Ces valeurs correspondent à la série TTL standard. Autrement dit, le courant maximal qui

entre par une entrée TTL standard dans l’état HAUT est I

IHmax

= 40 µA, et le courant

maximal qui quitte une entrée TTL standard dans l’état BAS est I

ILmax

= 1,6 mA.

Sortance à l’état bas =

mA 1,6

I

I

I

maxOL

maxIL

maxOL

=

(en U.L.)

Sortance à l’état haut =

A 40

I

I

I

maxOH

maxIH

maxOH

µ

=

(en U.L.)

Même si ces facteurs de charge sont ceux de la série standard, on les utilise quand même

pour exprimer les exigences d’entrée et les capacités d’attaque de la sortie de toutes les

séries TTL.

Entrance (fan in) :

Entrance à l’état bas =

mA 1,6

I

maxIL

(en U.L.)

Entrance à l’état haut =

A 40

I

maxIH

µ

(en U.L.)

10

Page 8 sur 15

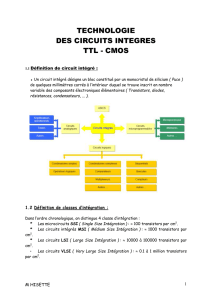

Comparaison des paramètres de différentes familles de logique TTL

Tension d’alimentation = 5 V

Température ambiante = 25 °C

Capacité de charge = 15 pF

TTL CMOS

74

74L

74F

74S

74AS

74LS

74ALS

74HC

4000B

V

OHmin

2,4 v

2,4

v

2,4 v

2,7 v

2,7 v

2,7 v

2,7 v

V

IHmin

2 v

2 v

2 v

2 v

2 v

2 v

2 v

V

OLmax

0,4 v

0,3

v

0,4 v

0,5 v

0,5 v

0,5 v

0,5 v

V

ILmax

0,8 v

0,8

v

0,8 v

0,8 v

0,8 v

0,8 v

0,8 v

Retard de

propagation

10

ns

33

ns

6 ns

3 ns 1,5

ns

9,5

ns

4 ns

7 ns

40 ns

Consommation

10

mW

1

mW

22

mW

19

mW

20

mW

2

mW

1 mW

<< <<

Marge de bruit

à l’état haut

à l’état bas

Sortance 40 20 50 50 50 20 20 10 2

Première génération

- 74 : normale ou standard, la première introduite sur le marché

- 74L : low power, faible consommation, applications lentes

- 74F : high speed, vitesse de commutation élevée

11

Deuxième génération

les transistors ne fonctionnent plus en saturation grâce aux diodes Schottky (faible seuil

0,25v) placées entre base et collecteur, ce qui réduit les temps de commutation.

- 74S: applications rapides

- 74LS : destinée à remplacer la série normale

Troisième génération

améliorations par réduction des capacités de jonction.

- 74AS : advanced Schottky ou F ( Fairchild advanced Schottky technology)

- 74ALS : advanced low power Schottky

12

Page 9 sur 15

Série 4000 – CIRCUITS INTÉGRÉS CMOS

Principe : utilisation des transistors CMOS (PMOS ET NMOS)

Caractéristique de transfert d'un inverseur CMOS

13

Page 10 sur 15

CMOS : Série 4000

Les circuits CMOS (série 4000) sont moins rapides que les circuits TTL mais ils ont une

consommation beaucoup moins importante.

A l'heure actuelle, ces différences tendent à s'estomper puisqu'on fabrique des TTL à faible

consommation et des CMOS rapides.

Entrées inutilisées :

Les entrées CMOS ne doivent jamais rester non branchées, mais raccordées au 0 V, au

VDD, à une autre entrée utilisée ou mises à la masse ou à VDD à travers une résistance.

En effet, une entrée non connectée capte les signaux parasites, ce qui peut se traduire par

une plus grande consommation et une surchauffe importante.

14

Page 11 sur 15

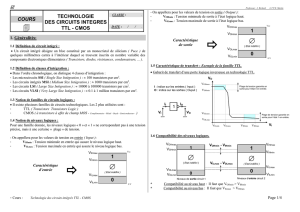

Caractéristiques des circuits

15

Page 12 sur 15

CMOS : Série 74

CMOS rapides (high speed CMOS) 74 H C x x et 74 H C T x x

CMOS classiques 74 C x x (technologie identique à la série 4000)

Les familles 74 HC et 74 HCT sont des circuits CMOS rapides et consommant trés peu

comme toutes les familles CMOS.

Elle se différencie de la famille CMOS 4000B par:

une tension d'alimentation comprise entre 2 V à 6 V

une grande rapidité

un plus grand courant de sortie, sortance plus élevée.

La famille 74 HC est caractérisée par une grande immunité aux bruits contrairement au

TTL et 74 HCT.

La famille 74 HCT est née d'un besoin de compatibilité des signaux entre les TTL et les

CMOS.

16

Page 13 sur 15

17

Page 14 sur 15

COMPATIBILITÉ D’ASSOCIATION DES CIRCUITS TTL ET CMOS

18

Page 15 sur 15

19

1

/

5

100%