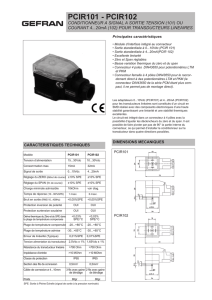

Caractéristiques générales des circuits intégrés

Introduction

Important de connaˆıtre les caract´eristiques des circuits

Diff´erences de comportement portes r´eelles ↔portes id´eales

ID´elai entre changement des entr´ees et mise `a jour de la sortie

(d´elai de propagation)

IBruit dans un circuit ´electronique peut r´eduire la fiabilit´e

ILimites de puissance une sortie ne peut fournir de signal `a plus de N

entr´ees

∃diff´erentes familles de circuits

⇒il faut choisir l’une `a la conception

IDiff´erents avantages et inconv´enients (ex.: vitesse, consommation, . . .)

IInterfacer diff´erentes familles est source de probl`emes . . .

Gammes diff´erentes de tension d’alimentation

Codage incompatible des niveaux logiques H / L

(ex: intervalles de tensions diff´erents)

I. . .mais int´eressant (ex: partie critique rapide et ´energievore, p´eriph´erie

plus lente et ´econome)

´

Electronique 1 (cours 3) Introduction |Technologies |Sp´ecifications 2 / 27

Introduction

Exemple: cons´equence du d´elai de propagation

&1

&2

a

b

z

cQ

a b c Q

. . .

H L L H

. . .

H H H H

Passage (a,b,c)=(H,H,H) `a (H,L,L) :

Chronographe

L

Ht

a

L

Ht

b

L

Ht

c

L

Ht

z

L

Ht

Q

delai de propagation d’une porte

Qne devrait pas

changer d’´etat !

´

Electronique 1 (cours 3) Introduction |Technologies |Sp´ecifications 3 / 27

Introduction

Plan du cours

Technologies principales et leurs caract´eristiques

Lire les donn´ees des fabricants

leadsto param`etres importants d’un circuit int´egr´e

ISeuils de dommages irr´eversibles

IParam`etres conseill´es de fonctionnement

ITol´erances sur les entr´ees/sorties

IComportement dynamique: temps de propagation

Circuits d’entr´ee/sortie particuliers

´

Electronique 1 (cours 3) Introduction |Technologies |Sp´ecifications 5 / 27

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

1

/

27

100%