MISE EN ŒUVRE D`UN PROCESSEUR 4BITS PAR SYNTHESE

27/04/2009

[

Copyright LAGIN GARY

]

M1 EEA

M

ISE EN ŒUVRE D

’

UN PROCESSEUR

4

BITS PAR

SYNTHESE LOGIQUE DE HAUT NIVEAU SUR

FPGA

Mise en œuvre d’un processeur 4 bits par synthèse logique de

haut niveau sur FPGA

LAGIN GARY M1 EEA Page 2

SOMMAIRE

I .Mise en place du décodeur d’instruction.......P4

II. Mise en place du décodeur d’instruction complet......15

III. Développement de la partie calcul...........P16

IV. Développement de la partie de contrôle....P17

Mise en œuvre d’un processeur 4 bits par synthèse logique de

haut niveau sur FPGA

LAGIN GARY M1 EEA Page 3

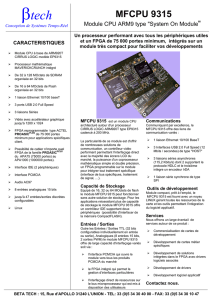

Présentation du projet

L e but de ce projet est de réaliser un microprocesseur 4 bits et d’implémenter la structure sur un

FPGA. On introduira ainsi les concepts élémentaires de l’architecture des microcontrôleurs.

Avantages du projet :

• Maitrise du logiciel Quartus.

• Progrès en langageVHDL.

• Notions de schémas bloc.

• Compréhension du principe de l’architecture d’un microprocesseur très simple qui sera

bénéfique si nous devions travailler sur une architecture plus complexe en entreprise.

• Autonomie d’apprentissage et explication des professeurs.

Inconvénient du projet.

• Durée des séances assez lourdes.

• Bug du logiciel Quartus qui nous fait perdre du temps.

Schéma de principe du microprocesseur.

Mise en œuvre d’un processeur 4 bits par synthèse logique de

haut niveau sur FPGA

LAGIN GARY M1 EEA Page 4

I .Mise en place du décodeur d’instruction

La première étape consistera à lire dans la mémoire de programme, l’instruction et sa donnée et de

faire parvenir l’instruction au bloc « MicroInstruction » (MI).

Nous mettrons en place les 3 blocs suivants que nous étudierons séparément :

• Le compteur de programme PC (PC.qpf)

• La mémoire de programme PM (PM.qpf)

• Le registre d’instruction RI (RI.qpf)

Nous commencerons à étudier et puis créer le bloc PC dont sa structure a déjà été vue en TD.

Etude du compteur de programme PC :

La commande PC est un pointeur qui va pointer et se déplacer par incrémentation sur les adresses de

la mémoire PM où le programme a été crée (par l’utilisateur).

Mise en œuvre d’un processeur 4 bits par synthèse logique de

haut niveau sur FPGA

LAGIN GARY M1 EEA Page 5

Ainsi :

Admettons le programme ci-dessous : (sens de lecture du programme de haut en bas) :

mnémonique

Instruction

& donnée

(sur 8 bits)

commentaire

LDA 2

0101|

0010

On charge 2 dans l’accu A

.

ADD 1

0010

|

0001

On addition le contenu par 1

.

OUT

0100|

0000

Le résultat est transmis

le

registre « output register ».

NOP

0000|

0000

Arrêt du programme

.

De plus, le cahier des charges nous informe que PC compte de 0000 à 1111 soit en décimal de 0 à 15

et que le pointeur est initialisé à 0.

Ainsi nous en déduisons une mémoire PM de 16 mots de 8 bits (capacité 128 bits).

Voici ce que cela nous donne :

Mémoire programme (PM)

Au début PC=0

0101 0010

PC+1

0010 0001

0100 0000

0000 0000

@0000

@0001

@0010

@0011

@0100

@1111

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%