Test 1 d`informatique 1 Nom:

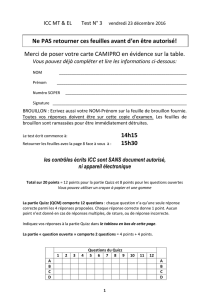

ICC MT & EL Test N° 3 vendredi 19 décembre 2014

Ne PAS retourner ces feuilles avant d’en être autorisé!

Merci de poser votre carte CAMIPRO en évidence sur la table.

Vous pouvez déjà compléter et lire les informations ci-dessous:

NOM ____________________________________________________________

Prénom _____________________________________________________________

Numéro SCIPER _________________________________________________________

Signature _______________________________________________________________

Le test écrit commence à: 14h15

Retourner les feuilles avec la dernière page face à vous à : 15h30

les contrôles écrits ICC sont SANS document autorisé,

ni appareil électronique

Total sur 20 points = 12 points pour la partie Quizz et 8 points pour les questions ouvertes

La partie Quizz (QCM) comporte 12 questions : chaque question n’a qu’une seule réponse

correcte parmi les 4 réponses proposées. Chaque réponse correcte donne 1 point. Aucun

point n’est donné en cas de réponses multiples, de rature, ou de réponse incorrecte. Indiquez

vos réponses à la partie Quizz dans le tableau en bas de cette page.

La partie « question ouverte » comporte 2 questions. Chaque question rapporte 4 points.

Questions du Quizz

1

2

3

4

5

6

7

8

9

10

11

12

A

A

B

B

C

C

D

D

1

QUIZZ

Question 1 : quel circuit a pour sortie X selon la table

de vérité suivante ->

A

B

X

0

0

1

0

1

1

1

0

0

1

1

0

Réponse : A B C D

--------------------------------------------------------------------------------------------------------------------------

Question 2 : Quelle est la table de vérité de la sortie X

de ce circuit ->

A

B

X

0

0

1

0

1

1

1

0

1

1

1

0

A

B

X

0

0

1

0

1

0

1

0

1

1

1

1

A

B

X

0

0

0

0

1

1

1

0

1

1

1

1

A

B

X

0

0

1

0

1

1

1

0

0

1

1

1

Réponse : A B C D

2

Question 3 : on désire réduire le temps pour effectuer une addition sur 64 bits par un facteur

de (presque) 4. L’idée est de gagner un facteur 2 supplémentaire par rapport à la solution vue

en cours en remplaçant les additionneurs sur 32 bits par des additionneurs sur 16 bits. Combien

faut-il d’additionneurs 16 bits en tout ?

A

B

C

D

3

15

7

16

--------------------------------------------------------------------------------------------------------------------------

Question 4 : un laptop est équipé d’un processeur avec un niveau de mémoire cache (latence

10ns), une mémoire centrale (latence 150 ns) et un disque dur (latence 1ms). On observe la

répartition suivante des accès aux données lorsqu’on travaille sur une tâche T : 60% des accès

aux données tirent parti de la mémoire cache ; pour les autres accès, 90% sont obtenus de la

mémoire centrale tandis que le reste doit être demandé au disque dur.

Quelle est la latence moyenne (en ns) pour cette tâche T ?

A

B

C

D

100

40’060

181

100’141

-----------------------------------------------------------------------------------------------------------------------------

Le programme assembleur suivant est exécuté avec une valeur entière strictement positive

disponible dans le registre r0. Le résultat est chargé dans r4.

Voici quelques précisions sur des instructions pouvant présenter une ambiguïté :

cont_egal a, b, c fait continuer l’exécution à la ligne c si les registres a et b sont égaux.

divise ra, rb, rc effectue la division entière de rb par rc et range le résultat dans ra

0 : charge r1, 1

1 : charge r2, 0

2 : charge r3, 2

3 : cont_egal r0, r1, 7

4 : divise r0, r0, r3

5 : somme r2, r2, r1

6 : continue 3

7 : charge r4, r2

8 : stop

Question 5 : Lorsque r0 vaut 9 comme valeur initiale, le résultat de l’exécution est :

A

B

C

D

2

3

4

1

Question 6 : quel est l’ordre de complexité de ce programme en fonction de r0 ?

A

B

C

D

O(1)

O(r0)

O(r02)

O(log(r0))

3

Question 7 :

Ce graphe de routeurs Internet

montre la distance entre chaque

nœud à coté de chaque lien. Par

exemple, la distance entre A et B

est de 3. Indiquer quelle est la

table de routage du nœud C

parmi les choix suivants. Pour

chaque destination (colonne de

gauche) on indique la direction

du prochain nœud (colonne du

milieu) et la distance du plus

court chemin (colonne droite).

Dest.

Dir.

Dist.

A

A

8

B

B

4

D

D

3

E

E

1

Dest.

Dir.

Dist.

A

B

7

B

E

3

D

B

3

E

E

1

Dest.

Dir.

Dist.

A

E

6

B

E

3

D

E

2

E

E

1

Dest.

Dir.

Dist.

A

E

6

B

E

3

D

D

3

E

E

1

Réponse : A B C D

--------------------------------------------------------------------------------------------------------------------------

Question 8 : on considère un réseau contenant plusieurs routeurs (A,B, C, …, N). On connaît

seulement les tables de routage des nœuds A, F et H données ci-dessous :

A

F

H

Dest.

Dir.

Dist.

Dest.

Dir.

Dist.

Dest.

Dir.

Dist.

G

B

2

K

N

3

D

G

2

D

C

2

L

E

2

F

N

2

N

x

y

J

I

2

J

N

3

En se basant uniquement sur les informations fournies par ces tables et sur la règle de

mémoriser seulement le plus court chemin dans une table, indiquer les valeurs correctes de x

et de y :

A

B

C

D

x = C et y = 4

x = B et y = 5

x = C et y = 5

x = B et y = 4

4

Question 9 : supposons que l’EPFL soit reliée à d’autres nœuds du réseau suisse comme ceci :

Le réseau comporte 5 nœuds :

EPFL, UniBe, ETHZ, UniSG, USI.

Les tables ci-dessous indiquent

seulement la direction du nœud

suivant pour une destination, ou

un ensemble de destinations

données. Dans cette question, on

peut remarquer que le chemin

entre deux nœuds n’est pas

déterminé par le plus petit

nombre de sauts. En effet, les

tables prennent en compte aussi

la capacité des liens. Par exemple,

la capacité du lien EPFL -> USI n’est pas suffisante pour supporter la bande passante requise

pour les communications entre EPFL et ETHZ, c’est pourquoi les communications EPFL->ETHZ

passent par UniBe comme première étape, puis par USI car les liens UniBe->USI et USI->ETHZ

ont une plus grande capacité (remarque : un centre de calcul important est installé à USI).

Enfin, il faut aussi remarquer que la capacité des liens dépend de la direction de transmission,

ce qui explique qu’une communication entre deux sites ne va pas forcément utiliser le même

chemin dans les deux sens. Voici les tables :

EPFL

UniBe

ETHZ

USI

UniSG

Dest.

Dir.

Dest.

Dir.

Dest.

Dir.

Dest.

Dir.

Dest.

Dir.

UniBe,

ETHZ,

UniSG

UniBe

EPFL

EPFL

UniSG

UniSG

EPFL

EPFL

ETHZ

ETHZ

USI

USI

USI,

ETHZ,

UNISG

USI

UniBe

UniBe

UniBe

UniBe

USI,

UniBe,

EPFL

USI

EPFL,

USI

USI

ETHZ,

UniSG

ETHZ

Indiquer la bonne réponse pour une communication établie entre l’EPFL et UniSG dans les

deux sens :

A

B

C

D

EPFL->UniBe->USI->ETHZ->UniSG et UniSG->ETHZ->USI->UniBe->EPFL

EPFL-> USI-> UniSG et UniSG->USI->EPFL

EPFL-> USI-> UniSG et UniSG->ETHZ->USI->UniBe->EPFL

EPFL->UniBe->USI->ETHZ->UniSG et UniSG->USI->EPFL

--------------------------------------------------------------------------------------------------------------------------

Question 10 : Soit un ordinateur avec un processeur d’horloge 2 GHz et une mémoire cache

de 16 blocs, chaque bloc ayant une taille de 128 octets. La mémoire centrale présente une

latence de 100 cycles d’horloge du processeur. On désire exécuter un programme pour traiter

séquentiellement un ensemble de données de 8 KiB (c'est-à-dire 213 octets) présent en

mémoire centrale. Le programme lit un octet à la fois et accumule sa valeur dans un registre

du processeur. On considère que cette accumulation (=addition) représente un cycle

d’horloge du processeur. Quel est le temps nécessaire pour réaliser cette tâche ?

A

B

C

D

8192 ns

3200 ns

4146 ns

7296 ns

5

6

6

7

7

8

8

9

9

10

10

1

/

10

100%