2. Logique Séquentielle

Royaume du Maroc

OFFICE DE LA FORMATION PROFESSIONNELLE ET DE LA PROMOTION DU TRAVAIL

Première Année

Programme de Formation des Techniciens Spécialisés en

Électronique

DIRECTION DE LA RECHERCHE ET INGENIERIE DE LA FORMATION

Novembre 1995

MODULE 05

Systèmes Logiques & Numériques

Résumé de Théorie

Télécharger tous les modules de toutes les filières de l'OFPPT sur le site dédié à la formation professionnelle au

Maroc : www.marocetude.com

Pour cela visiter notre site www.marocetude.com et choisissez la rubrique : MODULES ISTA

TABLE DES MATIÈRES

2. LOGIQUE SÉQUENTIELLE 2-1

2.1 Introduction à la logique séquentielle 2-1

2.2 Les Familles Logiques 2-1

2.2.1 Fonctionnement TTL 2-1

2.2.2 Avantages et Inconvénients du Totem Pole 2-2

2.2.3 Impédances 2-3

2.2.4 Niveaux Logiques 2-4

2.2.5 Types de boîtier et gamme de température 2-4

2.2.6 Feuilles Caractéristiques TTL 2-5

2.2.7 Portes logiques à collecteur ouvert («open collector«) 2-6

2.2.8 TTL Schottky (74S) 2-8

2.2.9 TTL Low Power Schottky (74LS) 2-8

2.2.10 Famille CMOS 2-8

2.2.11 Niveaux logiques CMOS 2-9

2.3 Circuits à base de logique séquentielle 2-10

2.3.1 Les Bascules 2-10

2.3.2 Entrées asynchrones 2-13

2.3.3 Les Compteurs 2-13

2.3.4 Les Multivibrateurs 2-16

2.3.5 Analyse de Systèmes Numériques 2-16

2.4 Exercices 2-17

Résumé de Théorie Systèmes Logiques & Numériques

Logique Séquentielle Page 2-1 OFPPT/TECCART

2. Logique Séquentielle

2.1 Introduction à la logique séquentielle

Ce module permet de développer et d’approfondir des compétences en logique

combinatoire et séquentielle. Jusqu’à présent, lors des analyses et des réalisations de

travaux pratiques, les composants étaient idéaux, mais la réalité est tout autre. Il est

nécessaire de consulter les fiches techniques du manufacturier afin de s’assurer que leurs

limites sont respectées. Pour ce faire, nous caractériserons les familles logiques TTL et

CMOS. L’analyse mathématique est un outil important pour la modélisation de nos

systèmes numériques. Il s’avère primordial de développer cet aspect d’analyse par la

conversion et les opérations arithmétiques dans les bases décimale, binaire, hexadécimale

et les codes BCD8421, ASCII ... À partir des schémas blocs et électriques, l’analyse des

circuits séquentiels terminera le module. Les éléments tels que les bascules, les

compteurs, les registres et les oscillateurs (astables et monostables) nécessitent une bonne

compréhension des chronogrammes de fonctionnement et l’utilisation constante des

caractéristiques du manufacturier.

2.2 Les Familles Logiques

2.2.1 Fonctionnement TTL

La famille TTL (Transistor-Transistor-Logic) est caractérisée par un transistor d’entrée à

émetteur multiple et de transistors de sortie formant une configuration dites «Totem

Pole». Tous les transistors fonctionnent suivant le régime de saturation-coupure.

VCC

A

BS

D1 D2

4k 1k6 130R

D3

Q3

Q4

Q2

1k

Émetteur 1

Émetteur 2

Base

Collecteur

Q1

Figure 2-1

Résumé de Théorie Systèmes Logiques & Numériques

Logique Séquentielle Page 2-2 OFPPT/TECCART

Les transistors Q3 et Q4 forment le «Totem pole» de sortie. Q2 est le transistor qui active

cette sortie et Q1 est le transistor à émetteur multiple dont chacun des émetteurs est

comparable à une diode.

Le circuit de la Figure 2-1 accomplit une fonction NON-ET dont la partie ET est

accomplie par les deux émetteurs de Q1. Lorsqu’une des entrées A ou B (ou les 2) est à

un niveau logique 0, Q1 est à VCESAT (typiquement 0.2V) et cette tension apparaît à la

base de Q2, ce qui maintient ce dernier à coupure. Q2 étant à coupure, aucun courant ne

circule dans ce transistor, ce qui empêche REQ2 de chuter du potentiel et empêche Q4 de

conduire. Cependant, le potentiel retrouvé au collecteur de Q2 est suffisamment élevé

pour faire conduire Q3 et, ainsi, assurer un niveau logique 1 à la sortie.

Lorsque les entrées A et B sont toutes deux à un niveau logique 1, les jonctions base-

émetteur de Q1 ne conduisent pas. Cependant, la jonction base-collecteur de Q1 est

polarisée en direct, ce qui permet la polarisation du transistor de Q2. Q2 étant conducteur,

une tension d’environ 0.6V se retrouve aux bornes de la résistance de 1K, cette dernière

étant en parallèle avec la jonction base-émetteur de Q4. Le transistor Q4 conduit.

Lorsque le transistor Q2 est en conduction, on retrouve à son collecteur une tension de

0.8V; puisque la résistance de 1K chute 0.6V et que Q2 conduit, le VCE de ce dernier

chute à 0.2V., on retrouve donc un voltage de 0.8V à la base de Q3. Si on regarde, à la

sortie de la porte logique, on aperçoit que D3 est en série avec la jonction base-émetteur

de Q3. Il faut environ 1.4V à la base du transistor Q3 pour que celui-ci puisse conduire.

Cette tension étant égale à 0.8V, Q3 est bloqué. Un niveau bas apparaît à la sortie par

l’entremise de Q4.

2.2.2 Avantages et Inconvénients du Totem Pole

L’avantage d’une sortie «Totem Pole» est qu’il n’y a qu’un seul des deux transistos de

sortie qui fonctionne à la fois. Si le transistor du haut fonctionne, celui du bas est bloqué;

et l’inverse, si le transistor en bas fonctionne, celui du haut est bloqué. À la sortie,

l’impédance est toujours faible puisqu’un transistor en conduction a un Rth faible et est

toujours en parallèle avec un transistor bloqué qui a un Rth élevé.

Cependant, la sortie «Totem pole» engendre du bruit avec Vcc et le point commun pour la

raison suivante. En condition statique, l’un des transistors de sortie en «Totem» est saturé

tandis que l’autre est coupé. Lors d’une transition, les deux transistors passent par leur

région linéaire c’est-à-dire qu’ils sont tous les deux en partie sous tension pendant un

instant. Il s’en suit que les parasites sont induits sur les lignes d’alimentation. Pour

réduire les parasites, il est recommandé d’installer un condensateur de 0.01 F entre Vcc

et commun pour chaque groupe de huit circuits intégrés ou moins.

Résumé de Théorie Systèmes Logiques & Numériques

Logique Séquentielle Page 2-3 OFPPT/TECCART

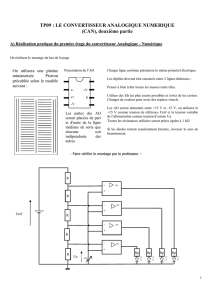

2.2.3 Impédances

Impédance d’entrée

VCC

A

B

4k

Q1

Figure 2-2

Zin = Impédance d’entrée vue par A ou B.

Zin = Résistance statique de la diode base-émetteur base de Q1+résistance de base,

divisée par

Résistance statique: très faible valeur par rapport à la résistance de base.

Zin = Rb / en commutation est très faible.

in = Rb

Zin = 4K

Impédance de sortie

L’impédance de sortie a déjà été discutée à la section précédente.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

1

/

19

100%