3. Programmer les entrées/sorties en mode simple.

Royaume du Maroc

OFFICE DE LA FORMATION PROFESSIONNELLE ET DE LA PROMOTION DU TRAVAIL

Première Année

Programme de Formation des Techniciens Spécialisés en

Électronique

DIRECTION DE LA RECHERCHE ET INGENIERIE DE LA FORMATION

Septembre 1995

MODULE 11

Introduction aux Microprocesseurs

Résumé de Théorie

Télécharger tous les modules de toutes les filières de l'OFPPT sur le site dédié à la formation professionnelle au Maroc :

www.marocetude.com

Pour cela visiter notre site www.marocetude.com et choisissez la rubrique : MODULES ISTA

INTRODUCTION AUX MICROPROCESSEURS

RÉSUMÉ DE THÉORIE

Programmer les entrées/sorties en mode simple.

TECCART INTERNATIONAL 2000 inc.

3155, boul. Hochelaga,

Montréal, Québec (Canada)

H1W 1G4

RÉDACTION

Serge Leblanc.

DESSINS ET CONCEPTION GRAPHIQUE

Serge Leblanc

RÉVISION TECHNIQUE

Pierre Asselin B.Sc. & Christian Lépine

RÉVISION LINGUISTIQUE

François Gaudreau

COMMISSION DE VALIDATION

Formateurs de l'OFPPT

Les droits de reproduction et de diffusion de ce document sont cédés par Teccart

International 2000 inc. à l’Office de la Formation Professionnelle et de la Promotion

du Travail du Royaume du Maroc, pour sa propre utilisation au Maroc.

Mis à part l’OFPPT, toute reproduction, en tout ou en partie, par quelque procédé

que ce soit, est interdite.

Mp_Rt3.Doc, imprimé à Montréal, le 17 avril 2017

TABLE DES MATIÈRES

3. PROGRAMMER LES ENTREES/SORTIES EN MODE SIMPLE. 3-1

3.1 Description générale du PIA 3-1

3.2 Brochage du PIA 3-1

3.2.1 Signaux réservés aux données des péripheriques: 3-2

3.2.2 Signaux réservés aux données du microprocesseur: 3-2

3.2.3 Signaux de contrôle et de synchronisation avec les périphériques: 3-2

3.2.4 Signaux de controle et de synchronisation avec le MPU: 3-2

3.3 Branchement du PIA sur le système Mod. E6809 3-3

3.4 Les registres du PIA 3-3

3.5 La programmation du PIA 3-4

3.6 Tableau résumé des fonctions du registre CRA du PIA 3-6

3.7 Choisir et installer un interface de puissance 3-7

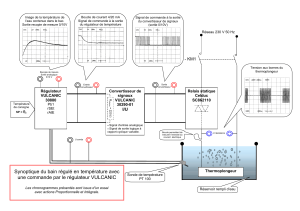

3.8 Commande d’un élément de puissance 3-9

3.8.1 Schéma bloc du système 3-9

3.8.2 Algorithme de traitement 3-10

3.8.3 Ordinogramme 3-10

3.8.4 Programme assembleur 3-11

3.9 Convertisseur numérique à analogique 3-12

3.9.1 Rappel 3-12

3.9.2 Schéma électrique du convertisseur N/A 3-12

3.9.3 Programme de contrôle du convertisseur N/A 3-13

3.9.4 Programme assembleur: 3-13

3.10 Convertisseur analogique à numérique 3-14

3.10.1 Schéma électrique du convertisseur A/N 3-14

3.10.2 Le circuit de mise à l’échelle du signal d’entrée 3-15

3.10.3 Le convertisseur analogique à numérique ADC0804 3-15

3.10.4 Programme de contrôle du convertisseur A/N 3-15

3.11 Exercices 3-17

Résumé de Théorie Introduction aux Microprocesseurs

Programmer les entrées/sorties page 3-1 OFPPT/TECCART

3. Programmer les entrées/sorties en mode simple.

3.1 Description générale du PIA

Le PIA (abréviation de Peripheral Interface Adaptor) est un circuit électronique

sophistiqué qui contrôle des périphériques reliés en parallèle. Tous les micro-ordinateurs

travaillent avec des circuits d'entrées/sorties pour assurer la liaison avec le monde

extérieur. Le PIA est incorporé dans bon nombre d'applications commandées par divers

types de microprocesseurs. Ce circuit d'entrée/sortie peut recevoir des contacts simples ou

disposés en matrice, contrôler des lecteurs de LED, des relais ou des opto-coupleurs, etc.

Le PIA est incontestablement très populaire comme interface.

Le PIA communique avec les périphériques via 16 lignes d'entrée/sortie. Ces lignes PAO

à PA7 et PBO à PB7 sont configurées en 2 ports PA et PB de 8 bits (8 lignes). Un port

constitue un groupe d'entrées/sorties parallèles. Chaque ligne est programmée séparément

en entrée ou en sortie. Le programmeur peut contrôler chaque ligne de sortie

individuellement et lire l'état de chaque ligne d'entrée; c'est une question de logiciel !

Ainsi, quand le programmeur lit le port PA programmé en entrée, l'état des 8 lignes PAO

à PA7 est acheminé à travers le PIA puis sur les lignes DO à D7 du bus de données

jusque vers le microprocesseur. Quand le programmeur écrit dans le port B, programmé

en sortie, l'information est envoyée par le microprocesseur via le bus de données (lignes

DO à D7) puis à travers le PIA jusque sur les lignes PBO à PB7 du port B.

Les différences entre le port A et le port B se situent au niveau des possibilités d'échange

avec protocole entre le PIA et les péripheriques. Le port A est mieux adapté aux entrées

tandis que le port B convient mieux aux sorties. Chaque port est doté de 2 lignes de

contrôle: l'une en entrée (CA1 ou CB1) et l'autre en entrée ou en sortie (CA2 et CB2).

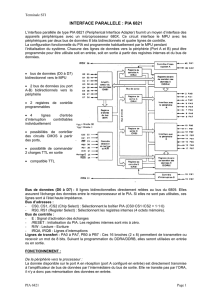

3.2 Brochage du PIA

La figure ci-contre montre le brochage du PIA.

Voici un résumé des signaux et du brochage du

PIA. D’un point de vue fonctionnel, les signaux

appartiennent à 4 catégories.

Signaux réservés aux

données des

périphériques

PA0 à PA7

PB0 à PB7

Signaux réservés aux

données P.

D0 à D7

Signaux de contrôle et

de synchronisation avec

les périphériques.

CA1, CA2

CB1, CB2

Signaux de contrôle et

de synchronisation avec

le microprocesseur.

E, R/W, /RESET CS0,

CS1, /CS2 ,RS0, RS1

/IRQA, /IRQB

Figure 3-1

VSS

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

CB1

CB2

VCC

CA1

CA2

/IRQA

/IRQB

RS0

RS1

/RESET

D0

D1

D2

D3

D4

D5

D6

D7

E

CS1

/CS2

CS0

R//W

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

M

C

6

8

2

1

Résumé de Théorie Introduction aux Microprocesseurs

Programmer les entrées/sorties page 3-2 OFPPT/TECCART

3.2.1 Signaux réservés aux données des péripheriques:

PA0- PA7 Port A lignes d'entrée ou de sortie (logique à 3 états).

PB0 PB7 Port B lignes d'entrée ou de sortie (logique a 3 etats).

Ces lignes ne supportent pas de transferts bidirectionnels de données. Chaque ligne peut

fournir en source 1mA à 1.5 V et conduire la base d'un transistor. En entrée, chaque ligne

est à l'état 0, si la tension appliquée est de 0.8 V et moins et à l'etat 1, si la tension

appliquée est de 2 V et plus. Une ligne du port B (assigné en sortie) entre en état de haute

impédance lors d'une lecture.

3.2.2 Signaux réservés aux données du microprocesseur:

DO - D7 Lignes du bus de données assurant le transtert bidirectionnel d'information

entre le microprocesseur et le PIA. Ces lignes fonctionnent en logique à 3

états.

3.2.3 Signaux de contrôle et de synchronisation avec les périphériques:

CA1 Ligne, en entrée seulement, utilisée pour signaler une cause d'interruption

d'un périphérique.

CA2 Lorsque CA2 est programmée en entrée. cette ligne fonctionne comme

CA1. Lorsque CA2 est programmée en sortie, elle est utilisée comme

signal de réponse sur les données reçues au port A.

CB1 Ligne, en entrée seulement, utilisée pour signaler une cause d’interruption

d'un périphérique.

CB2 Lorsque CB2 est programmée en entrée, cette ligne fonctionne cornme

CB1. En sortie, elle véhicule un signal associé à l’envoi de données sur le

port B.

3.2.4 Signaux de controle et de synchronisation avec le MPU:

E Signal de synchronisation d’horloge avec le MPU.

R/W Si R/W = 1, le MPU lit dans le PIA les données provenant des

périphériques où il lit les registres DDRA, DDRB, CRA ou CRB.

Si R/W = O, le MPU écrit des données dans le PIA pour les envoyer aux

périphériques où il programme les registres DDRA, DDRB, CRA et CRB.

/IRQA et Lorsque ces deux signaux passent à l'état logique 0, ils signalent une

/IRQB demande d'interruption provenant du PIA. Les broches /IRQA et

/IRQB sont généralement connectées aux lignes d’interruptions du CPU.

/RESET Signal qui remet à 0 les registres internes du PIA. Lors d'un reset, les ports

A et B sont en entrée.

CS0, CS1 et /CS2 : Le boîtier du PIA sera choisi si CSO = 1, CS1 = 1 et CS2 = O.

RSO et RS1 Ces 2 lignes donnent accès aux 6 registres internes du PIA; 4 registres sont

accessibles directement et les 2 autres le sont de façon indirecte.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

1

/

21

100%