E_1_edc_tp_eleve

B.3.3 Introduction à la commutation

Bernaud J. 1/7

1°) Transistor fonctionnant en interrupteur commandé : Commutation

(fonctionnement bloqué, saturé)

1.1) Rappels

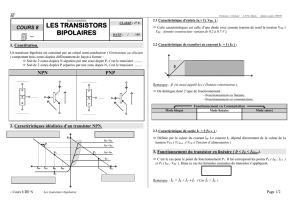

T1 transistor 2N1711, RC = 1,8 kVCC = 15 V, VBB = 5 V,VBE = 0,6 V, min = 100.

Déterminer l’équation de la droite de charge :

Placer sur un graphe IC = f(VCE) la droite de charge, le point de fonctionnement à l’état

bloqué (B) et à l’état saturé (C).

Calculer la valeur de RB, pour pouvoir saturé le transistor à coup sûr.

Rb

Vbb

Vcc

Rc

Vce

Ic

Vbe

Ib

E

C

B

Vce (V)

Ic (mA)

Ib (µA)

B.3.3 Introduction à la commutation

Bernaud J. 2/7

Faire le montage et vérifier que le transistor est saturé.

1.2) Modélisation du transistor

Etat bloqué Etat saturé

1.3) Puissance consommée

à l’état bloqué: p = ,

à l’état saturé: p =.

En commutation, en considérant le transistor comme parfait, on peut

donc dire que sa consommation en énergie est très faible.

1.4) Expérience

Remplacer la source de tension par un G.B.F (sortie TTL) générant un

signal en créneaux comme suit: fréquence : 1 kHz.

Visualiser à l’oscilloscope vbb(t) et vce(t).

Tracer leur graphe respectif.

vbb (V)

t(ms)

T

5

t(ms)

vbb (V)

5

T

Etat du transistor

vce

B.3.3 Introduction à la commutation

Bernaud J. 3/7

Faire varier la fréquence du signal d’entrée, tracer les nouveaux graphes pour f = 100 kHz.

On définit: ton : temps de croissance,

toff : temps de décroissance.

Que devient à cette fréquence la puissance consommée par le transistor?

1.5) Conclusion

2°) Comparaison de deux familles de portes logiques T.T.L ( LS ) et C.M.O.S

2.1) Généralités:

De plus en plus, l’électronique utilise des composants caractérisés par deux états de

fonctionnement (« ouvert » et « fermé »). A ces deux états, on fait correspondre deux états

logiques notés « 0 » et « 1 ».

Les portes logiques sont les constituants de base; à chacune d’elle correspond une

fonction logique. Les principales fonctions sont les fonctions NON, ET, OU, NON ET, NON

OU, OU EXCLUSIF.

A chaque fonction correspond un symbole et une table de vérité.

NON ET OU OU exclusif NON ET NON OU

S = S = S = S = S = S =

Ecrire les tables de vérité de chaque fonction logique:

E S E1 E2 S E1 E2 S E1 E2 S E1 E2 S E1 E2 S

1

&

> 1

= 1

&

> 1

E

S

S

E2

E1

B.3.3 Introduction à la commutation

Bernaud J. 4/7

A quelle fonction logique, le transistor étudié précédemment correspond-il?

En pratique, on utilise souvent des portes universelles, telles que NON ET (NAND) et

NON OU (NOR) qui permettent, en les associant correctement de recréer n’importe quelle

fonction logique.

Exemples:

Réaliser une porte OU à partir de NON ET.

2.2) Caractéristiques des deux familles de portes logiques (valeurs à 25°C)

2.2.1) Famille T.T.L (Transistor.Transistor.Logic) 74LS00

Elle se caractérise par une tension d’alimentation de 5 V.

Une durée de commutation des portes très brève : 9,5 ns.

Un courant d’entrée non nul.

Une puissance consommée en statique de l’ordre de 2mW, et similaire

en dynamique à 100 kHz.

2.2.2) Famille C.M.O.S (Complementary.Métal.Oxyde.Semiconductor) 4011B

Elle se caractérise par une tension d’alimentation de 3 V à 14 V.

Une durée de commutation des portes de l’ordre de 40 ns.

Un courant d’entrée nul.

Une puissance consommée en statique de l’ordre de 1µW, et de 0,1 mW en

dynamique à 100 kHz.

2.3) Mesures:

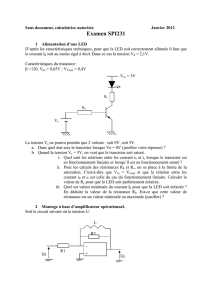

Dans toute la mesure, on utilisera les circuits intégrés TTL 74LS00 et CMOS

4011B (quadruple porte NAND).

Avant de commencer les mesures, tester les portes en vérifiant la table de vérité.

B.3.3 Introduction à la commutation

Bernaud J. 5/7

&

&

&

&

1

VDD

CMOS 4011

&

&

&

&

1

VCC

TTL 74LS00

2.3.1) Caractéristiques de transfert en tension

Montage: utiliser le + 5 V de la carte Synchronie

Tracé de la caractéristique vs = f(ve) porte TTL:

Pour générer ve utiliser Synchronie (Paramètres, Sortie) définir une

dent de scie évoluant entre 0 et 5V, acquérir le signal vs sur la voie EA0, que vous

renommerez, la sortie étant ouverte Dans la fenêtre Paramètres, onglet Acquis régler la durée

totale sur 10 s.

Pour quelles valeurs de Ve peut-on considérer que le niveau de sortie est un niveau

logique bas (noté 0)?

Idem pour un niveau logique de sortie haut (1)?

Comparer aux valeurs données par le constructeur :

Indiquer sur le tracé les domaines donnés par ce dernier pour niveau bas et haut.

Tracé de la caractéristique vs = f(ve) porte CMOS:

Faire la mesure avec Vdd = 5 V.

Faire la même démarche que pour la porte TTL, en veillant à cocher

dans la rubrique Paramètres onglet Acquis : Ajouter courbes

Pour quelles valeurs de Ve peut-on considérer que le niveau de sortie est un niveau

logique bas (noté 0)? Idem pour un niveau logique de sortie haut(1)?

Comparer aux valeurs données par le constructeur, indiquer sur le tracé les domaines

donnés par ce dernier pour niveau bas et haut.

&

vs

ve

+5 V

6

6

7

7

1

/

7

100%