III MISE EN OEUVRE DES CIRCUITS INTEGRES

TECHNOLOGIE DES CIRCUITS INTEGRES LOGIQUES - D ANGELIS

65

VII MISE EN OEUVRE DES CIRCUITS INTEGRES

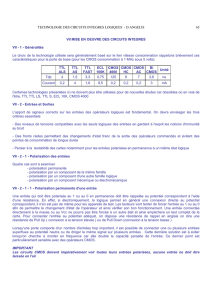

VII - 1 - Généralités

Le choix de la technologie utilisée sera généralement basé sur le lien vitesse consommation rappelons brièvement ces

caractéristiques pour la porte de base (pour les CMOS consommation à 1 MHz sous 5 volts):

TTL

ALS

TTL

AS

TTL

FAST

ECL

100K

CMOS

4000

CMOS

HC

CMOS

AC

Bi

CMOS

Unité

Tdp

4

1,5

3,3

0,75

125

9

7

3,8

ns

Courant

0,2

4

1,6

9,5

0,2

0,2

0,2

3

mA

Certaines technologies présentées ici ne doivent plus être utilisées pour de nouvelles études car obsolètes où en voie de

l'être, TTL TTL LS, TTL S, ECL 10K, CMOS 4000

VII - 2 - Entrées et Sorties

L'apport de signaux corrects sur les entrées des opérateurs logiques est fondamental. On devra envisager les trois

critères essentiels:

- Des niveaux de tensions compatibles avec les seuils logiques des entrées en gardant à l'esprit les notions d'immunité au

bruit

- Des fronts raides permettant des changements d'état franc de la sortie des opérateurs commandés et évitant des

pointes de consommation de longue durée

- Penser à la testabilité des cartes notamment pour les entrées polarisées en permanence à un même état logique

VII - 2 - 1 - Polarisation des entrées

Quatre cas sont à examiner

- polarisation permanente

- polarisation par un composant de la même famille

- polarisation par un composant d'une autre famille logique

- polarisation par un composant mécanique ou électromécanique

VII - 2 - 1 - 1 - Polarisation permanente d'une entrée

Une entrée qui doit être polarisée au 1 ou au 0 en permanence doit être rappelée au potentiel correspondant à l'aide d'une

résistance. En effet, si électroniquement, la logique permet en général une connexion directe au potentiel correspondant, il

n'en est pas de même pour les appareils de test. Les testeurs vont tenter de forcer l'entrée au 1 ou au 0 afin de permettre

le changement d'état de l'opérateur et ainsi vérifier son bon fonctionnement. Une entrée connectée directement à la

masse ou au Vcc ne pourra pas être forcée à un autre état et ainsi empêchera un test complet de la carte. Pour connecter

l'entrée au potentiel adéquat, on dispose une résistance de rappel en anglais on dira une résistance de Pull Up (

connexion à la tension élevée ) ou de Pull Down (connexion à la tension basse )

Lorsqu'une porte comporte d'un nombre d'entrées trop important, il est possible de connecter une ou plusieurs entrées

superflues au potentiel neutre ou de diriger le même signal sur plusieurs entrées . Cette dernière solution est à éviter

lorsqu'on cherche à monter en fréquence car elle double la capacité parasite de l'entrée. Ce dernier point est

particulièrement sensible avec des opérateurs CMOS.

IMPORTANT

Les circuits CMOS doivent impérativement voir toutes leurs entrées polarisées, aucune entrée ne doit être laissée

en l'air

TECHNOLOGIE DES CIRCUITS INTEGRES LOGIQUE - D ANGELIS

66

Montage à éviter pour

qui veut monter en

fréquence

Montage avec

résistance de rappel au

Vcc "pull up"

Montage avec résistance de

rappel à la terre "pull down"

Fig VII - 1 - Entrées avec résistance de rappel

Détermination de la valeur de la résistance

La valeur de la résistance à disposer doit fournir un potentiel compatible avec les états logiques désirés. Le calcul de la

résistance se fera à partir de la chute de tension provoquée par le courant de polarisation ou la valeur sera choisie de

façon à ce que l'entrée présente la meilleure immunité au bruit

CMOS au 1 ou au 0 logique l'entrée de ces circuits consomment peu cependant on limitera la valeur des résistances de

rappel à quelques Kilo-ohms

TTL au 1 logique ces circuits consomment peu les résistances de rappel pourront prendre des valeurs de quelques

Kilo-ohms

au 0 logique le problème est plus délicat, en effet le courant débité n'est pas négligeable et la tension maximale

admissible est de 0,8volt. On essaiera d'obtenir 0,4 volt pour une bonne immunité au bruit

IIL

R40,

TTL

AS

ALS

FAST

IIL

0,5 mA

0,2 mA

0,6 mA

R maxi (pour 0,4V)

800 Ω

2000Ω

670Ω

ECL Les entrées de ces circuits sont connectées par une résistance interne de 50kΩ à VEE de ce fait il est

possible de laisser une entrée non connectée.

VII - 2 - 1 - 2- Polarisation par un composant de la même famille

VII - 2 - 1 - 2 - 1 - Les CMOS

Les circuits d'une même famille sont conçus pour être mis bout à bout sans problème la question est de savoir combien

d'entrées pourront être connectées à une même sortie

Pour les CMOS , la sortie se comporte comme une résistance et l'entrée comme une capacité en série avec une

résistance. Le temps d'établissement d'un état logique dépendra du RC ainsi constitué. Lorsqu'une sortie alimente

plusieurs entrées c'est autant de capacités mises en parallèle et donc un ralentissement. En statique, une entrée ne

consomme pratiquement rien aussi une sortie peut étre connectée à un nombre considérable d'entrées mais la vitesse de

commutation sera très lente.

TECHNOLOGIE DES CIRCUITS INTEGRES LOGIQUES - D ANGELIS

67

Le temps de commutation dépendant de la charge est un des paramètres les plus en défaveur de la série 4000

puisqu'il interdit toute évaluation de la fréquence maximale d'un circuit tant que le schéma n'est pas achevé.

Nous avons vu page 49 que la sortie d'une porte de la série 4000 alimentée sous 5volts est assimilable à une résistance

de 500 Ω et l'entrée à une capacité de 5pF en série avec une résistance de 1500 Ω ce qui donne une constante de temps:

σ =RC = 2000.5.10-12 = 10-8seconde ou 10 nS

Lorsqu'une sortie pilote 10 entrées nous plaçons 10 résistances de 1500 Ω en parallèle ainsi que 10 condensateurs de 5

pF soit une résistance équivalente de 150 Ω en série avec une capacité de 50pF et la résistance de sortie de 500 Ω. La

constante de temps devient:

σ =RC =.(500+150).50.10-12 = 3,25.10-8seconde ou 32,5 nS.

La fréquence maximale d'utilisation est alors de quelques Mégahertz ( 3 à 4)

La série 4000 étant en voie d'abandon, nous ne nous étendrons pas plus sur ce sujet.

Les CMOS HC et AC , sont notablement différents sur ce plan, la résistance de sortie a été divisée par 10 et la résistance

de 1500 0 en série avec la capacité, d'entrée a disparue. La valeur de la capacité d'entrée est restée identique

Fig VII - 2 - Sortie et Entrée des portes HC et AC

La constante de temps est considérablement plus faible et les fréquences utilisables beaucoup plus élevées ainsi, la

fréquence maximale de l'horloge d'une bascule JK alimentée sous 5volts sera:

TECHNOLOGIE

FREQUENCE

74C76

4 MHz

74HC76 ou 74HC109

25 MHz

74AC109

175 MHz

La sortance des circuits CMOS est une question de fréquence. A basse fréquence plusieurs dizaines d'entrées peuvent

être connectées à une sortie cependant il convient de ne pas trop détériorer le temps de montée (rise time ) ou le temps

de descente (fall time). Lors du changement d'état d'une sortie d'opérateur, un transistor se bloque pendant que l'autre

devient passant durant cette transition la résistance de ces deux éléments en série entre Vdd et Vss (l'alimentation) peut

tomber à 600 Ω on comprend qu'il n'est pas raisonnable de prolonger la durée de cet appel de courant. Il est possible

également qu'une variation trop lente du signal d'entrée d'un opérateur provoque des oscillations sur sa sortie. Un temps

de transition maximal des signaux appliqués sur les entrées est généralement précisé par le fabricant

TECHNOLOGIE DES CIRCUITS INTEGRES LOGIQUE - D ANGELIS

68

Un autre paramètre est à prendre en considération, il s'agit du temps de transition des signaux appliqués sur les entrées,

un maximum est précisé par le fabricant, le signal devra être conforme.

Le tableau ci-dessous donne les temps de transition maxi des signaux à appliquer ainsi que les temps de montée et de

descente des signaux de sortie de ces mêmes opérateurs.

Si nous comparons ces données pour une alimentation de 5 Volts:

la CMOS 4000 réclame 15 μS et fournit tr = 180 nS tf = 100 nS

la CMOS HC réclame 500 nS et fournit tr = 8 nS tf = 8 nS

la CMOS AC réclame 40 nS et fournit tr = 4 nS tf = 2 nS

On voit que la CMOS 4000 ne doit pas piloter un circuit AC

TECHNOLOGIE

Temps de

transition maxi

sur les entrées

Temps de transition du

signal de sortie

(typique sur 50 pF)

TENSION

D'ALIMENTATION

15 μs

tr = 180 nS tf = 100 nS

5 Volts

CMOS 4000

5 μs

tr = 90 nS tf = 50 nS

10 Volts

4 μS

tr = 65 nS tf = 40 nS

15 Volts

1000 ns

38 nS

2 Volts

CMOS HC

500 nS

8 nS

4,5 Volts

400 nS

6 nS

6 Volts

150 nS/V

3,0 Volts

CMOS AC

40 nS/V

tr = 4 nS (sur 5 Volts)

4,5 Volts

25 nS/V

tf = 2 nS (sur 5 Volts)

5,5 Volts

VII - 2 - 1 - 2 - 2 - Les TTL

Une entrée de circuit TTL ne consomme pratiquement rien au 1 Logique seul le 0 logique pose problème. Une entrée au

zéro logique débite un courant qui peut étre important la tension maximale produite par ce courant ne doit pas dépasser

0,8 Volt. Afin de conserver une immunité au bruit suffisante on s'efforcera de ne pas dépasser 0,4 volt.

Le nombre d'entrées connectables à une sortie est déterminé en divisant le courant de sortie à l'état bas IOL (courant qui

peut être absorbé par le transistor T4 du schéma ci-dessous) par le courant débité par une entrée IIL (courant passant par

la jonction base émetteur de TI)

Fig VII – 3 – Connexion d’une sortie TTL avec une entrée

TECHNOLOGIE

IOL max

IIL max

SORTANCE

TECHNOLOGIE DES CIRCUITS INTEGRES LOGIQUES - D ANGELIS

69

Std

16 mA

1,6 mA

10

S

20 mA

2,0 mA

10

LS

8 mA

0,36 mA

22

AS

20 mA

0,5 mA

40

ALS

8 mA

0,2 mA

40

FAST

20 mA

0,6 mA

33

Le mélange des technologies est tout à fait possible, les niveaux de tension étant identiques il suffira d'utiliser les valeurs

de IOL et de IIL adéquat quant aux temps de transition, ils ne sont pas très différents et ne posent pas de problèmes en

cas de mélange de technologies à l'intérieur de la famille TTL

Temps de montée

Temps de descente

TECHNOLOGIE

tr

tr

Std

12 nS

5 nS

S

6 nS

3 nS

LS

13 nS

3 nS

AS

5 nS

3 nS

ALS

10 nS

6 nS

FAST

2 nS

2 nS

VII - 2 - 1 - 3 - Polarisation par un composant d'une autre famille

Il n'est généralement pas recommandé de mélanger les technologies, chacune ayant son domaine d'application. La

technologie CMOS 4000 n'est pas directement compatible avec la TTL mais pourra cependant s'interfacer sans trop de

difficulté, la connecter avec l'ECL serait une démarche curieuse car les vitesses sont tellement différentes qu'on ne voit

pas la justification d'une telle association. Les nouvelles technologies CMOS , HC et AC s'interface facilement avec les

composants TTL à l'aide de leurs séries HCT et ACT , vitesses, consommations, tensions d'alimentations sont proches,

les deux familles peuvent voisiner sans gros problèmes. La famille ECL par ses tensions d'alimentation spécifiques

s'interface plus difficilement avec les deux familles précédentes, il sera nécessaire de translater les états logiques ce qui

complique sérieusement la chose, la connexion entre ECL et portes GaAs semble avoir été prévue notamment par Gigabit

qui préconise des tensions d'alimentation ECL pour ses portes logiques GaAs, cependant les portes GaAs n'abondent pas

sur le marché dans l'état actuel aussi il nous est difficile de généraliser et surtout de prévoir l'avenir du GaAs.

VII - 2 - 1 - 3 - 1 - Association CMOS 4000 ↔ TTL

Examinons les problèmes posés par une association telle que ci-dessous (les inverseurs peuvent être remplacés par des

portes quelconques) l'inverseur ne possédant qu'une entrée simplifie le problème:

Fig VII – 4 – Association d’inverseurs CMOS 4000 et de TTL pour une mise en évidence des problèmes

Mise en regard des tensions de sortie et d'entrée des opérateurs logiques:

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

1

/

14

100%