marques.william

MARQUES William

DEBITON Nicolas

1

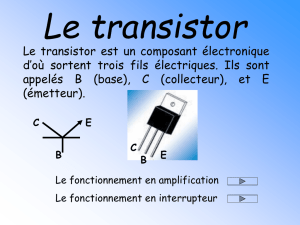

TRANSISTOR MOS

Applications analogiques

But du TP : Nous désirons visualiser les différentes caractéristiques d’un transistor

MOS à l’aide des différentes applications.

1. Caractéristiques du transistor NMOS

Nous désirons visualiser les caractéristiques Id=f(Vgs) à Vds=2.5V(constante) et

Id=f(Vds) pour Vgs=2.5V.

Nous déterminons ces courbes à l’aide du logiciel Spice.

Les caractéristiques obtenues sont les suivantes :

Id=f (Vds)

Pour Vgs=2.5V, la transconductance (pente de la courbe dans la zone de saturation)

gm=0.4mA/V.

Zone ohmique

MARQUES William

DEBITON Nicolas

2

Id=f (Vgs)

Nous relevons Vto=1.20V tension de seuil du transistor.

2. Amplificateur NMOS

2.1 Caractéristique de transfert « grand signal »

Nous désirons étudier la variation de la tension de sortie Vs (drain du transistor) en

fonction de Ve (tension grille-source).

Nous réalisons le montage suivant :

Remarque : Le substrat pour un NMOS doit être relié à la masse.

Grandeurs utilisées pour ce montage :

-Vdd=5V ; R=10kΩ ;

-Ve=signal triangulaire de fréquence 100Hz et variant de 0 à 5V.

a. Visualisons Vs=f (Ve)

Nous utilisons le mode XY de l’oscilloscope et relevons l’oscillogramme suivant :

Vto=1.20V

MARQUES William

DEBITON Nicolas

3

b. Nous distinguons donc les différentes zones de fonctionnement du transistor.

A noter que pour réaliser un amplificateur grâce à ce transistor, il faut polariser celui-

ci dans la zone pincée. Le maximum d’amplification sera obtenu si nous polarisons le

transistor autour du centre du « segment » de la zone pincée (la pente est maximum

au milieu du « segment »).

c. Nous réalisons ce même montage mais en le simulant à l’aide de Spice :

L’oscillogramme est le suivant :

Nous observons donc une courbe identique à l’étude expérimentale.

X= 500 mV/div

Y= 1 V/div

Zone

bloquée

Zone

pincé

e

Zone

ohmique

Amplification

max

Amplification

max

Zone bloquée

Zone pincée

Zone ohmique

MARQUES William

DEBITON Nicolas

4

2.2 Utilisation en amplification « petit signal »

a. Nous désirons réaliser la fonction « amplification linéaire » grâce au transistor, il

faut donc le polariser au milieu de la partie linéaire de la zone pincée. (Amplification

maximale).

Nous réalisons pour ce faire le montage suivant :

Caractéristiques du circuit :

-Vdd=5V ; Ve=signal sinusoïdal de fréquence 1kHz dont l’amplitude doit être

déterminée expérimentalement pour obtenir Vs sans déformation.

-R1=100kΩ R2=10kΩ ;

-C1=100nF (correspondant à une fréquence de coupure basse de 100Hz).

Déterminons la valeur de la résistance R2 afin de polariser le transistor pour le point

de fonctionnement précédent : Vs=3V et Ve=2.3V.

Le courant dans R1 et R2 sont quasiment identique puisque le courant de grille du

MOS est pratiquement nulle. Nous pouvons donc appliquer la règle du pont diviseur.

Vg= (Vdd*R2) / (R1+R2) Vg*R1 + Vg*R2 = Vdd*R2 R2 = (Vg*R1) / (Vdd – Vg)

R2= 83 kΩ.

b. Nous utilisons un potentiomètre (R2) et réalisons cette polarisation de manière

expérimentale. Nous relevons R2=88 kΩ et Vdso=3.4V. Ces valeurs diffèrent

légèrement des valeurs théoriques, différences dues aux imprécisions

expérimentales.

c. Nous désirons déterminer l’amplification à vide. Nous utilisons le modèle « petits

signaux » du transistor.

Nous avons rd=1/gd très supérieur à R. Nous pouvons donc considérer la résistance

rd comme étant un circuit ouvert.

L’amplification à vide A= Vs / Ve = (-gm*Vgs*R) / (Vgs) = -gm*R

MARQUES William

DEBITON Nicolas

5

Or gm=0.4 mA/V et R=10 kΩ A= -4.

Remarque : Le MOS sature lorsque Vs = 5V= Vdd, il ne faut donc pas appliquer une

tension supérieur à (Vdd/A) 1.25V afin de ne pas observer de saturation sur Vs.

Nous relevons expérimentalement une amplification de -3.7V. La légère différence

entre la valeur théorique et pratique provenant des imprécisions de mesures ainsi

qu’à l’imperfection du transistor.

d. L’oscilloscope utilisé durant ce TP ne nous permettait pas de déterminer le taux de

distorsion. Nous avons pu néanmoins le visualiser sur un oscilloscope METRIX où

nous nous sommes aperçus que plus Ve augmentait plus le taux de distorsion est

important pour cause de linéarité imparfaite de la zone pincée.

e. Nous désirons vérifier nos résultats en simulant ce montage à l’aide de Spice.

Nous relevons dans ce cas une amplification A= -3.7. (Quasi similaire au résultat

précédent ; le signe « -« correspondant à un déphasage de 180° entre Ve et Vs).

Imprécisions du au fait que nous avons négligé la résistance de sortie du transistor

rd.

Les taux de distorsion pour les différentes valeurs de Ve s’obtiennent en réalisant

une FFT à l’aide de Spice et en visualisant le fichier de sortie Output file. Nous

obtenons alors :

-Ve=100 mV taux de distorsion= 1.51%

-Ve=200 mV taux de distorsion= 2.48%

-Ve=400 mV taux de distorsion= 8.21%

Ce qui confirme que plus Ve augmente plus le taux de distorsion augmente.

6

6

7

7

8

8

9

9

10

10

1

/

10

100%