projet - CEA-Irfu

Date de mise à jour : 28/02/07

FICHE PROJET : CMS Electronique

Resp. Scientifique : M. Dejardin

Chef de Projet : I. Mandjavidze

EOTP : A-CMSXX-03-03

Ordre Statistique :

Thématique/Programme : Les constituants ultimes de la matière/La physique au

LHC

1- Enjeux scientifiques/Concurrences :

L’objectif majeur du projet CMS Electronique est le développement d’un dispositif

électronique nommé le processeur de lecture sélective pour le calorimètre

électromagnétique de l’expérience CMS au CERN (SRP – Selective Read-out

Processor). Le SRP fait partie de l’électronique de lecture du calorimètre dit

« Hors–Détecteur » dû à son implantation dans la caverne de service souterraine

hors de la caverne d’expérimentation. Pour chaque événement accepté par le

premier niveau du système de déclanchement de l’expérience, le SRP doit

permettre à alléger en temps réel la quantité des données brutes du calorimètre

avant leur envoi vers le système d’acquisition. En dépit d’un facteur de réduction

considérable (de 15 à 20) à obtenir, la performance physique du calorimètre ne

doit pas être compromise.

2- Localisation/Mise en service : CERN, Genève/2007

3- Collaboration/Management/Responsabilités Dapnia:

La conception et la réalisation de l’électronique « Hors–Détecteur » sont

partagées entre les laboratoires suivants :

o CERN : cartes de configuration de l’électronique frontale et de distribution

d’horloge et de divers signaux de contrôle ;

o DAPNIA : cartes du processeur de lecture sélective SRP

o LLR Palaiseau+CERN : cartes de génération des primitifs de trigger

o LIP Lisbonne : cartes des mémoires tampon

Le Dapnia assure la coordination de la collaboration Electronique « Hors–

Détecteur » au CERN : J.L. Faure

Les responsabilités du Dapnia sont :

- Etude des algorithmes de lecture sélective

- Définition de l’architecture globale du dispositif de lecture sélective

- Définition des liens de communication du SRP avec d’autres sous systèmes de

l’électronique de lecture « Hors–Détecteur »

- Conception et réalisation du SRP

- Fourniture de 20 châssis VME pour l’ensemble de l’électronique « Hors–

Détecteur »

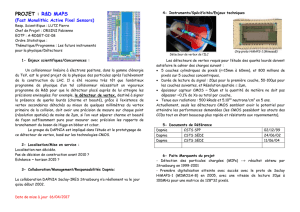

4- Instruments/Spécificités/Enjeux techniques

- Nombre considérable de liens d’entrée/sortie du SRP : ~200

- Débit élevé des liens : 1.6 Gbit/s (voir 2.5 Gbit/s) par lien

- Fonctionnement asynchrone à la fréquence du trigger de niveaux 1 : 100 kHz

- Budget temporel limité : 6 µs

- Flexibilité en choix d’algorithmes de sélection

- Réalisation à l’aide de la logique câblée programmable de type FPGA

- Liens de communications à base de la technologie d’optique parallèle

- 12 cartes VME 6U :

5- Documents de Référence

Dapnia

Réunion d’avancement du projet CMS Détecteur

16/06/03

CERN

Electronics System Review

05/05/04

Dapnia

Réunion d’avancement du projet CMS Electronique

15/06/06

CERN

SRP Electronics System Review

09/11/06

6- Faits Marquants du projet

Juin 2004 : Validation des liens de communications à base de la technologie

d’optique parallèle et de la contrainte temporelle de 5µs.

Décembre 2006 : Fin de la phase de prototypage et lancement de la production

1

/

1

100%