Les techniques de gestion des E/S Généralités La connexion d`un

L

LE

ES

S

T

TE

EC

CH

HN

NI

IQ

QU

UE

ES

S

D

DE

E

G

GE

ES

ST

TI

IO

ON

N

D

DE

ES

S

E

E/

/S

S

I. GENERALITES

La connexion d'un périphérique avec l'unité centrale requiert la mise en place d'une

interface. On distingue trois techniques pour établir une communication entre les

périphériques et l'unité centrale :

la scrutation

les interruptions

l'accès direct à la mémoire

1. La scrutation ou spolling

Périodiquement, le processeur va interroger chaque dispositif pour savoir si il a besoin

d'un service. Si un périphérique requiert un service, la routine va être enclenchée. Le

processus qui consiste à interroger un dispositif et à reçevoir une réponse en retour

s'appelle le « handshaking »

Cette technique est avantageuse car elle est facile à mettre en place. Mais le système

perd du temps à scruter tout les périphériques.

2. Les interruptions

Avec cette technique, c'est chaque dispositif qui va informer le processeur qu'il a

besoin de quelque chose par l'intermédiaire d'un bus système. A la fin de chaque

instruction, le processeur teste s'il y a eu une demande d'interruption.

Pour le processeur, gérer l'interruption consiste à

accepter la demande d'interruption : l'acceptation ou le refus d'une interruption

dépend de la valeur du bit IF (Interrupt enable Flag).

identifier la demande d'interruption : cette identification peut être faîte de

façon matérielle, logicielle ou la combinaison des deux.

Identification matérielle : un composant matériel, le contrôleur d'interruptions

va reçevoir les interruptions puis les relayer au processeur. Si ce dernier les

accepte, le contrôleur d'interruptions va placer sur le bus de données l'adresse qui

identifie le périphérique demandeur.

Identification logicielle : lorsqu'une interruption intervient, le processeur va

scruter chaque périphérique pour savoir lequel a déclenché cette interruption.

Identification combinée : pas compris.

traiter l'interruption : pour traiter l'interruption, le processeur va sauvegarder le

contexte du processeur, traiter l'interruption puis restituer le contexte.

Exemple avec les interruptions du 8086 :

Cette architecture gère deux types d'interruptions :

les interruptions internes : elles interviennent lors d'une divison par zéro ou

d'une erreur d'overflow, mais peuvent aussi placer le processeur dans un mode

particulier, comme le fonctionnement pas à pas.

Les interruptions externes : reset. Une interruption est déclenchée en cas de

baisse de tension.

3. L'accès direct à la mémoire

L'inconvénient des interruptions est qu'il est souvent nécessaire de rajouter des

éléments matériels pour la gestion des interruptions. De plus, les transferts de données sont

réalisés de façon logicielle, ce qui pénalise ses échanges.

Cette technique d'accès direct à la mémoire résoud en partie ce problème en

remplaçant une partie du traitement logiciel par un traitement matériel.

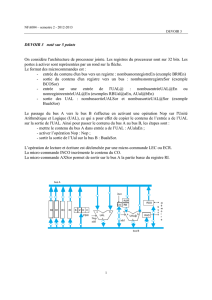

Le principe est de placer le processeur en veille, c'est à dire que le processeur place ces

bus à l'état « haute impédance », tout se passe alors comme s'il n'existait plus. Un

composant spécialisé, le DMAC (Direct Memory Access Controller) prend le contrôle du

bus système et gère le transfert d'informations avec une vitesse qui ne sera alors limitée

que par celle de la mémoire.

Pour mettre en veille le processeur, le DMAC va envoyer le signal HOLD au

processeur. Si le processeur accepte sa mise en veille, il envoie HOLDA vers le DMAC.

On peut alors avoir deux types de transferts :

le transfert de mémoire à mémoire : dans ce cas, le DMAC gère le transfert

avec trois registres : deux pour les adresses sources et destination, et un pour stocker la

donnée temporairement.

le transfert de périphérique à mémoire : ici les données ne transitent plus par

le DMAC, ce dernier ne fait que fournir les adresses et les signaux de lecture ou

d'écriture.

Cette technique d'utilisation de l'accès direct à la mémoire s'appelle le « DMA par la

mise en veille du processeur ». Il existe deux autres techniques de mise en oeuvre de

l'accès direct à la mémoire :

le DMA par vol de cycles : le processeur n'est pas mis en veille, il est

simplement ralenti. L'horloge du processeur est en partie détournée au profit du

DMAC.

le DMA multiplexé (ou DMA simultané) : Le DMAC va profiter des périodes

pendant lesquelles le processeur n'accède pas aux bus pour transférer les données.

Méthode complexe, d'autant plus qu'elle requiert un DMAC spécifique au processeur.

1

/

2

100%