Document

Maxime Augerd Page 1 SE 2004

Systèmes d’exploitation

Chapitre 1 : Généralités

A : INTRO

- Un OS c’est :

un ensemble de programmes qui se charge de tous les problèmes liés à l’exploitation de

la machine.

Objectifs : - faciliter la tâche des utilisateurs, optimiser l’utilisation des composants de

la machine.

Point de vue externe :

Il s’agit de :

- masquer à l’utilisateur les problèmes de gestion interne des ressources

- présenter une machine virtuelle plus simple à exploiter que la machine réelle

- offrir des services

But du noyau : isoler les applicatifs du matériel.

Point de vue interne :

Il s’agit de :

- gérer au mieux les unités fonctionnelles (CPU, mémoire etc.) qui compensent la

machine

- offrir un ensemble d’opérations de bas niveau que les programmes applicatifs peuvent

invoquer

Unités fonctionnelles :

Processeur : Traiter

Mémoire centrale : Mémoriser

E/S : Communiquer

Une instruction a plusieurs phases : Fetch, Decode, Execute, Store. Paradigme séquentiel ( on fait

les choses les unes après les autres ).

Maxime Augerd Page 2 SE 2004

Maxime Augerd Page 3 SE 2004

Architecture de machine :

L’architecture d’une machine c’est l’organisation de ses unités fonctionnelles

On ne retient dans un premier temps qu’une architecture d’interconnexion classique dans laquelle

un processeur, une mémoire centrale et les dispositifs d’E/S sont reliés par un bus.

L’OS doit donc optimiser l’utilisation des ressources et gérer les problèmes liés au

partage de ces ressources.

Vision d’un O.S. :

Dépend du niveau d’observation

Pour l’utilisateur il s’agit d’un ensemble de fonctionnalités offertes soit grâce à un

langage de commandes, soit à travers une interface graphique

Pour le développeur l’OS n’est qu’un ensemble d’appels systèmes qui fournit des

services de bas niveau ( ex : API WIN 32 )

Pour l’administrateur l’OS est un ensemble complexe de ressources à gérer et à

configurer ( espace disque, comptes utilisateurs, droits et protections, etc. )

B : Définitions :

Processus : suite d’instructions chargée totalement ou partiellement en mémoire centrale, et

constituant un ensemble logique en cours d’exécution ou susceptible de s’exécuter.

Notion dynamique : un processus naît lors du chargement d’un programme et meurt à l afin de

l’exécution du programme. Un processus est caractérisé par un état à un instant donné.

Programme : entité composée de séquences d’instructions agissant sur un ensemble de données.

C’est du code obtenu par compilation d’un fichier source suivie d’une phase d’édition des liens.

Notion essentiellement statique car c’est un fichier stocké sur disque.

Des processus distincts peuvent exécuter un même programme (programme réentrant).

Thread : un processus peut être parfois décomposé en unités d’activités distincts appelées thred et

qui :

s’exécutent de façon parallèle ou concurrente

partagent l’espace d’adresse du processus

Le processus représente donc pour ses threads une unité d’encapsulation des ressources utilisées.

Et le thread est un sous-ensemble d’exécution du processus sur cet ensemble de ressources.

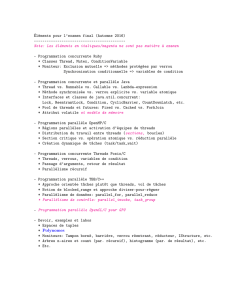

Thread : pour exploiter le parallèlisme

Tâche : nous conviendrons que la tâche représente la plus petite unité sémantique d’exécution au

niveau macroscopique. Donc suivant les systèmes :

une tâche = un processus sur les systèmes multi-processeurs

une tâche = un thread sur les systèmes multi-threads

Typologie des systèmes :

Système en mono ( obsolète )

Système multi-tâches :

o Plusieurs tâches résident en mémoire centrale

o L’OS doit alors gérer l’attribution et le partage des ressources entre les

différentes tâches.

Pose les problèmes liés à la programmation concurrente

Pose les problèmes de protection du code et des donnée

Système multi-threads :

o Supporte l’exécution d’un processeur en unités indépendantes

o Implémente au niveau du noyau la gestion des threads

o L’ordonnancement se fait alors sur des threads et non plus des processus

o Possibilité d’ordonnancer les threads sur plusieurs processeurs dans une

architecture parallèle

o Ex : Win NT

Système temps réel :

o Système dans lequel il existe des interactions entre le système et des

équipements (capteurs, actionneurs etc.)

Maxime Augerd Page 4 SE 2004

o Avec des contraintes de temps fortes d’origine matérielle entre l’occurrence

d’un évènement et la réponse appropriée du système à cet événement

Transactionnel et Temps Réel :

Un système temps réel est un système déterministe par opposition au système transactionnel de

l’informatique de gestion.

dans un système temps réel le temps de fin d’exécution d’une tâche est contraint

dans un système transactionnel le temps d’exécution d’une tâche dépend de l’activité

du système et du temps de réponse de l’utilisateur

Ceci impacte les stratégies d’ordonnancement des tâches suivant la nature du système

Mode d’utilisation :

Mode différé :

il s’agit d’un traitement par lots ( Batch Processing )

un lot = ensemble de programmes préparés avec leur données

les lots sont placés en file d’attente et exécutés séquentiellement

on peut aussi exécuter dans ce mode des fichiers de commandes

Mode intéractif :

dans ce mode toute action de l’utilisateur est traitée immédiatement par le système

2 types :

o time sharing : les utilisateurs ont accès simultanément à l’ensemble des

ressources, le système gère l’allocation cyclique des ressources

o le transactionnel : principal mode en informatique de gestion : il s’agit

d’applications qui gèrent le dialogue homme-machine suivant une logique liée

aux fonctionnalités attendues.

C – Les Fonctions d’un OS

Le chargement

Le système comprend généralement :

une partie toujours résidente en mémoire centrale et qui se nomme le noyau ( kernel )

une partie dynamiquement à l’exécution de la fonction demandée

Le chargement à la mise sous-tension s’effectue grâce à un programme chargeur simplifié appelé

BOOTSTRAP.

Principe :

le chargeur est automatiquement appelé au démarrage de la machine

pour cela il doit être stocké à une adresse disque convenue ( MBR ).

Permet de charger le noyau du système en mémoire centrale

Possible de changer le de chargeur

La génération système

Il s’agit du paramètrage d’un certain nombre d’éléments gérés par le système comme :

la taille de la zone de swap

la taille de la pagination

la taille des tampons utilisés pour les E/S ( entrées sorties )

les noms symboliques de périphériques

les protocoles d’échange

etc.

Permet de configurer le système.

Gestion de l’Unité Centrale :

La gestion de l’U.C. par l’OS consiste à :

planifier l’exécution des différentes tâches suivant une stratégie d’ordonnancement

assurer un mécanisme de commutation entre les tâches

Gestion de la mémoire centrale :

Il s’agit essentiellement :

d’allouer de l’espace mémoire aux tâches naissantes

Maxime Augerd Page 5 SE 2004

de charger les tâches à des adresse valides

d’assurer une non violation de l’espace mémoire alloué de chaque tâche

et de libérer l’espace mémoire des tâches terminées

Gestion des E/S :

Pour l’OS, traiter les E/S c’est desservir les demandes de transfert d’informations en

gérant des matériels divers ( CPU, interface d’E/S, contrôleur de périphériques, DMA,

périphériques )

en s’appuyant sur la mise en œuvre d’instructions privilégiées exécutées en mode

noyau pour les opérations de bas niveau

Autres fonctions :

Gestion des fichiers

l’organisation des supports ( logiques et physiques )

les accès aux fichiers

la protection et les droits d’accès aux fichiers

Gestion des utilisateurs

utilisateurs et droits et comptes etc.

dialogue homme-machine

Les utilitaires de service :

Outils d’administration :

configuration

exploitation

Outils d’aide à la production de programme

mesure et surveillance

droits et quotas

D – Comparatifs des OS

Les Windows : 9X, NT, 2000, XP, CE de Microsoft

MacOS d’Apple

La famille UNIX

HP/UX ( HP )

AIX ( IBM )

SunOS / Solaris ( SUN )

Unix-like : Linux, FreeBSD

OS/390 et Z/OS pour les MainFrame d’IBM

Chapitre 2 : Les interruptions ( rappel )

A : Qu’est ce qu’une interruption ?

- Une interruption consiste à suspendre la tâche en cours d’exécution pour exécuter autre

chose

- On appelle système d’interruptions la composante système qui prend en charge les

réponses appropriées aux demandes d’interruptions

- On distingue deux familles d’interruptions

Les IT Externes

Une IT externe est une IT asynchrone provoquées par un évènement sans relation avec les

instructions de la tâche en cours d’exécution.

Il s’agit d’une interruption matérielle générée par un dispositif externe.

On distingue :

défauts externes pour le traitement des erreurs matérielles

l’horloge utilisée pour le temps partagé

les E/S avec les périphériques

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

1

/

56

100%