I.Puissance dissipée par les transistors MOS : 1.Etude théorique de

I.Puissance dissipée par les transistors MOS :

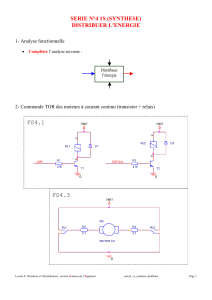

1.Etude théorique de la fonction FS32 : Interfacer en puissance au moyen d’une logique de

commande :

Si on polarise la grille d’un transistor PMOS par une tension négative, celui-ci est

saturé.

Pour obtenir le blocage de TR6, SPLUS = NL0, TR5 => bloqué

VGTR6 = VBAT VGSTR6 = 0V donc TR6 Bloqué

Pour obtenir la saturation de TR6, SPLUS = NL1, TR5 => saturé, on retrouve la masse à

VGTR6. Donc VGTR6 = 0V et VGSTR6 = - Vbat

Pour obtenir le blocage de TR3, SPLUS = NL0, TR2 => bloqué

VGTR3 = VBAT VGSTR3 = 0V donc TR3 Bloqué

Pour obtenir la saturation de TR3, SPLUS = NL1, TR2 => saturé, on retrouve la masse à

VGTR3. Donc VGTR3 = 0V et VGSTR3 = - Vbat

Si on polarise la grille d’un transistor NMOS par une tension positive, celui-ci est

saturé.

Si VGTR1 = NL1=> VGSTR1 = NL1, donc TR1 saturé

Si VGTR4 = NL1=> VGSTR4 = NL1, donc TR4 saturé

Le rapport cyclique de PWM varie en fonction de la vitesse. Plus la vitesse augmente, plus

l’état haut est long.

Le signal logique STOP est actif sur NL1.

VGTR4 = PWM.STOP.S+

STOP = NL1

S+ = NL1

VGTR4 = PWM

PWM commande le transistor.

2.Etude expérimentale de la fonction FS32 :

L’étude consiste à raccorder l’ensemble des deux cartes à l’attelle KINETEC.

On règle l’attelle en vitesse maximum pour la mobilisation puis on effectue :

les mesures des VDS ON des transistors PMOS à l’aide d’un multimètre

numérique selon les différents sens :

VDS ON TR6 = 0.17V VDS ON TR3 = 0.17V

les mesures des VDS ON des transistors NMOS à l’aide d’un multimètre

numérique selon les différents sens :

VDS ON TR1 = 0.2V VDS ON TR4 = 0.2V

3.Etude expérimentale de FS33 : convertir le courant moteur en tension :

On effectue les mesures de VMOT pour les deux sens de rotation du moteur à l’aide d’un

multimètre en conservant la vitesse maximum pour l’attelle :

VMOT (TR6, TR4 ON) = 142mV VMOT (TR3, TR1 ON) = 136mV

4.Réponse à la problématique :

PdTR6 = USD X IMOT = 165.10-3 X 0.7 = 0.1155W

PdTR4 = USD X IMOT = 275.10-3 X 47 = 0.19W

PdTR3 = USD X IMOT = 165.10-3 X 0.7 = 0.1155W

PdTR1 = USD X IMOT = 275.10-3 X 47 = 0.19W

Les TMOS fonctionnent en commutation, la puissance dissipée est donc très faible par rapport

à la puissance max admissible (43W). Il n’y a donc pas besoin de dissipation.

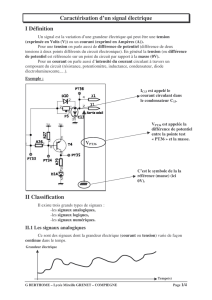

II.Etude structurelle de la carte alim:

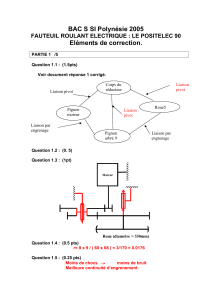

Schéma structurel :

Schéma fonctionnel de second degré :

1.Etude de FSA2 : Protéger et filtrer la tension :

Protections :

Le7568 fusible F1 1AT25 supporte le pic de courant pendant un court laps de temps et

protège des tensions négatives.

Le rôle de la diode PRO (SMT6 15A) est de limiter les tensions négatives en cas

d'inversement.

Filtrage :

Le rôle du condensateur C12 est de limiter les parasites.

Le rôle des condensateur C11, C38 et C40 est de lisser le signal (pour les condos polarisés)

électrolithique au tantale.

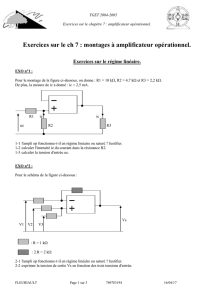

2.Etude de FSA3 : Générer une tension 5V régulée :

Protection et limitation en courant :

Le rôle de la diode D1 est d'empêcher les tensions négatives d'entrer dans le régulateur, les

inversions de polarités.

La raison pour laquelle les résistances R37 et R38 sont montées en dérivation est la limitation

de la puissance à dissiper.

Filtrage :

Le couple de condensateurs C39 et C18 sert à lisser le signal et éliminer les parasites.

Régulation à 5V :

D'après la fiche technique du 7805, les valeurs max et min de la tension d'entrée sont de 7 et

25V, le courant de sortie est de 1,5A, et la puissance maximale dissipée est de 2W.

A partir de ces valeurs, nous sommes en mesure de vérifier l'utilité et la valeur éventuelle d'un

refroidisseur :

P = Vmoy X Is

Vmoy = VinOUT – VinIN

Vmoy = 10,6 – 5 = 5,6V

Is = 25mA

P = 5,6V X 25mA = 0,14W < Pmax donc il n'y a l'utilité d'un refroidisseur.

3.Etude de FSA4 : Générer une tension image :

Voltage = (Vbat x R41) / (R40 + R41) = 0,32 x Vbat

C'est pour cette raison Voltage est une tension image de Vbat.

Le rôle joué par le condensateur C24 est de lisser la tension et enlever les parasites que génère

le moteur.

4.Etude de FSA5 : Générer une alimentation symétrique :

L'utilité du couple R39 et C22 dans l'élaboration de la tension V+ est de filtrer la tension pour

éliminer les parasites, il s'agit d'un filtre passe bas.

La fonction assurée par la fonction U5 est la conversion d'une tension positive en une tension

négative => V+ = -V-

Pour comprendre le fonctionnement de la structure de l'ICL 7660S, une simulation a été

réalisée et les courbes suivantes ont été relevé :

Validation par mesurage :

Pour valiser les mesures de la simulation, des mesures réelles ont été faites sur un cablage du

schéma.

Alimentation – génération de Vbat :

Vbat est à 12V en marche et à 11,6V en arrêt.

Alimentation – génération deVcc :

Pour Vcc à 5V dans un sens et dans l'autre, la tension à l'entrée du régulateur est de 10,6V et

10,5V.

FSA4 Génération d'une tension de référence :

La tension de référence mesurée pour Vbat est de 12V, comme spécifié dans le cahier des

charges.

FSA5 Alimentation – génération de V+ etV- :

Les tensions V+ et V- sont respactivement de 11V et -11V comme spécifié dans le cahier des

charges.

III.Etude structurelle de la carte micro :

1.Régler et acquérir les paramètres de fonctionnement :

Description des entrées/sorties :

Entrées :

- actions manuelles du kiné :

intervention sur les boutons de réglage

(extension, flexion, vitesse)

- actions manuelles du technicien :

intervention sur les 2 potentiomètres

permettant les réglages des valeurs limites de l’effort en extension et en flexion

- A2A1A0 :

6

6

1

/

6

100%