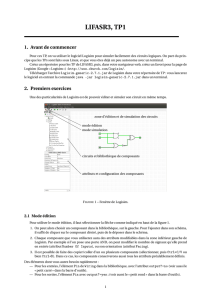

Systèmes Logiques Combinatoires: Additionneurs, Multiplexeurs

Telechargé par

Yassine AYAT

Systèmes Logiques

S.L-Iset Kass-Dép Elec-JLALI. F

28

Chapitre III:

Les systèmes combinatoires

III.1. Définition:

Un système logique est dit combinatoire lorsque ses fonctions de sortie sont complètement

définies par la connaissance des combinaisons des variables d'entrée, c'est à dire par les conditions

précisées par l'énoncé du problème. L'état des sorties ne dépend ainsi que de l'état actuel des

entrées.

III.2. Additionneurs:

III.2.1. Demi-additionneur:

Il s'agit d'additionner deux nombres A et B à 1 seul bit. Il présente deux sorties: S (somme) et

R (retenue).

Sa table de vérité est:

A

B

S

R

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

Les expressions logiques des sorties sont déduites directement à partir de la table de vérité:

BABABAS

BAR

D'après ces équations, un demi-additionneur est alors représenté par le logigramme suivant:

A

B

S

R

Systèmes Logiques

S.L-Iset Kass-Dép Elec-JLALI. F

29

Le schéma bloc est alors:

III.2.2. Additionneur complet à un seul bit:

Il s'agit d'additionner deux nombres A et B à un seul bit en tenant compte d'une retenue

antérieure Rn. Il présente deux sorties Sn et Rn+1.

A

B

Rn

Sn

Rn+1

0

0

0

0

0

1

0

0

1

0

0

1

0

1

0

1

1

0

0

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

1

1

1

1

1

1

nnnnn RBARBARBARBAS

)()( BABARBABAR nn

))()( BARBAR nn

Ainsi:

)( BARS nn

nnnnn RBARBARBARBAR

1

nnn RBABARRBA )()(

Ainsi:

nn RBABAR

)(

1

D'après ces équations, un additionneur complet à un seul bit est alors représenté par le

logigramme suivant:

1/2 +

A

B

S

R

Systèmes Logiques

S.L-Iset Kass-Dép Elec-JLALI. F

30

L'examen de ce logigramme fait apparaître deux demi-additionneurs et une porte OU. Ceci

permet de représenter le schéma bloc en utilisant des demi-additionneurs comme le montre la

figure ci-après:

Le schéma bloc d'un additionneur complet à un seul bit est alors

III.2.3. Additionneur de deux nombres à plusieurs bits:

Soient deux nombres A et B représentés sur n bits tels que

2021 )....( aaaA nn

2021 )....( bbbB nn

Pour additionner A et B, il faut additionner les bits

i

a

et

i

b

en commençant par ceux de plus

faible rang et en tenant compte des retenues. Donc, il faut regrouper en cascade n additionneurs

complets à un bit.

A

B

Sn

Rn+1

Rn

1/2 +

A

B

1/2 +

S

n

Rn+1

Rn

A.C à 1

bit

A

B

Sn

Rn+1

R

n

Systèmes Logiques

S.L-Iset Kass-Dép Elec-JLALI. F

31

Ainsi, un additionneur complet de rang i est modélisé par:

Remarque:

Il est évident que l'entrée R0 de l'additionneur à un bit de rang zéro est égale à zéro:

0

0R

.

Exemple: Additionneur de deux nombres à 4 bits

20123 )( aaaaA

;

20123 )( bbbbB

Ainsi, la somme s'écrit sous la forme suivante:

201234 )( SSSSRS

III.3. Soustracteurs:

III.3.1. Demi-soustracteur:

Il obéit aux quatre opérations de la soustraction binaire et possède deux sorties: la différence

des entrées A et B (A-B) et un empreint E. Il admet comme table de vérité

A

B

D

E

0

0

0

0

0

1

1

1

1

0

1

0

1

1

0

0

A . Complet

a

i

bi

Si

Ri+1

Ri

A.C3

a3

b3

S3

R4

R3

A.C0

a0

b0

S0

R1

0

A.C2

a2

b2

S2

R2

A.C1

a1

b1

S1

Systèmes Logiques

S.L-Iset Kass-Dép Elec-JLALI. F

32

Les expressions logiques des sorties sont déduites directement à partir de la table de vérité:

BABABAD

BAE

D'après ces équations, un demi-soustracteur est alors représenté par le logigramme suivant:

Le schéma bloc est alors:

III.3.2. Soustracteur complet à un seul bit:

Il s'agit d'effectuer la différence A-B de deux nombres A et B à un seul bit en tenant compte

d'un empreint antérieur En. Il présente deux sorties Dn et En+1.

A

B

En

Dn

En+1

0

0

0

0

0

1

0

0

1

0

0

1

0

1

1

1

1

0

0

0

0

0

1

1

1

1

0

1

0

0

0

1

1

0

1

1

1

1

1

1

nnnnn EBAEBAEBAEBAD

)()( BABAEBABAE nn

A

B

D

E

1/2 -

A

B

D

E

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

1

/

16

100%