FUBOCO: Structure Synthesis of Basic Op-Amps by FUnctional BlOck

COmposition

INGA ABEL and HELMUT GRAEB,

Technical University of Munich, Chair of Electronic Design Automation,

Germany

This paper presents a method to automatically synthesize the structure of an operational amplier. It is positioned between approaches

with xed design plans and a small search space of structures and approaches with generic structural production rules and a large

search space with technically impractical structures. The presented approach develops a hierarchical composition graph based on

functional blocks that spans a search space of thousands of technically meaningful structure variants for single-output, fully-dierential

and complementary operational ampliers. The search algorithm is a combined heuristic and enumerative process. The evaluation is

based on circuit sizing with a library of behavioral equations of functional blocks. Formalizing the knowledge of functional blocks in

op-amps for structural synthesis and sizing inherently reduces the search space and lessens the number of created topologies not

fullling the specications. Experimental results for the three op-amp classes are presented. An outlook how this method can be

extended to multi-stage op-amps is given.

Additional Key Words and Phrases: Analog circuit design, CMOS, operational ampliers,

ACM Reference Format:

Inga Abel and Helmut Graeb. 2021. FUBOCO: Structure Synthesis of Basic Op-Amps by FUnctional BlOck COmposition. 1, 1

(September 2021), 24 pages. https://doi.org/10.1145/nnnnnnn.nnnnnnn

1 INTRODUCTION

Automation of structural synthesis of analog circuits has not gained much attention from industry. A reason for this

might be that the current approaches are following two major paths, none of which seems to be attractive from the

industrial point of view. One path of structural synthesis is a specication-based selection of one or few netlists from a

library [

10

,

12

,

14

–

16

,

19

]. This is an automation of what happens in practice, as every company has a set of, say, 20

to 30 dierent netlists for op-amps, from which is initially chosen according to the specication. As an experienced

designer can do this selection instantly, there is little gain in design time or design quality. The other path of structural

synthesis builds up the netlist by combining modules of transistors and transistor groups while satisfying Kirchho

laws and basic voltage/current conversion at the module interfaces [

6

,

7

,

9

,

11

,

20

,

21

,

32

]. Here, a plethora of variants is

created, from which the promising ones are selected only after symbolic analysis and complete sizing. Designers see an

unnecessary variety of intermediate solutions that they would never have created. In the presented approach, a new

path for analog structural synthesis is started, which lies in the middle between these two poles. It does more than

selecting from 20 to 30 available alternatives. And it creates a much smaller number of intermediate solutions that fail

the requirements.

Authors’ address: Inga Abel, [email protected]; Helmut Graeb, [email protected], Technical University of Munich, Chair of Electronic Design

Automation, Arcisstr. 21, Munich, Germany.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not

made or distributed for prot or commercial advantage and that copies bear this notice and the full citation on the rst page. Copyrights for components

of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to

redistribute to lists, requires prior specic permission and/or a fee. Request permissions from [email protected].

©2021 Association for Computing Machinery.

Manuscript submitted to ACM

Manuscript submitted to ACM 1

arXiv:2101.07517v2 [eess.SY] 24 Sep 2021

2 Inga Abel and Helmut Graeb

Early topology synthesis approaches were [

11

,

15

,

19

]. While [

11

] was tested on dierent capacitor structures, as

LC-structures or switch-capacitors, [

15

,

19

] were developed for operational ampliers. In [

15

], a top level abstraction of

a circuit is implemented and hierarchically transformed into a transistor level structure with a xed design plan for

evaluation. [

19

] has a library of 64 topologies and xed design plans. Synthesis approaches based on genetic algorithms

followed to overcome the topology dependence of the early approaches [

6

,

9

,

14

,

20

]. They are based on libraries

containing simple transistor structures. With these methods, many dierent circuit topologies are created. However,

many topologies are redundant. To size the topologies and evaluate their practicability, simulations are used. To lessen

the number of redundant op-amp topologies, graph-grammar based approaches were developed [

7

,

21

,

32

]. With strict

grammar rules and isomorphism techniques, the number of redundant topologies are reduced. The evaluation and

sizing of the topologies takes place after synthesizing all possible topologies. Thus, much computation time is spent for

circuits which cannot fulll the given specications from a visual inspection of a designer. Other approaches to lessen

the number of created topologies were rule-based topology synthesis algorithms which closely implemented designer

knowledge [10, 12, 16].

Dierent to previous methods, the presented synthesis approach contains a comprehensive computer-oriented

systematic of op-amp functional building blocks like, e.g., amplication stages with their internal transconductances,

loads and biases. The functional blocks form a composition graph. Thus, it overcomes the topology dependency in

[

12

,

15

,

19

]. But it is still close enough to the op-amp structure such that redundant or impracticable topologies are

avoided. This makes algorithms to remove these structures as in [

21

,

32

] unnecessary. A novel algorithm for structural

synthesis iteratively composes op-amp netlists from these basic functional blocks. For given specications, the netlists

are evaluated using an analytical equation-based sizing method similar to [

3

]. A library was developed storing analytical

behavior models for every functional block in an op-amp [

4

]. Useless congurations are avoided in an early phase of

the structural synthesis process. For instance, there exist performance features which degrade if a second stage is added

to a one-stage op-amp topology, e.g., area, phase margin. In this case, the corresponding two-stage op-amp topology is

not created if the one-stage op-amp already indicates to fail these specications. Introducing design equations into the

structural synthesis process obviates the need for symbolic analysis [

11

] or circuit simulation [

20

,

31

] in evaluating

intermediate solutions. This is achieved by a rigorous adoption of the practical creation process of analog designers

along the functional block hierarchy of an operational amplier.

This paper is an extended version of [

1

]. [

1

] presented a prototype of the synthesis tool, creating up to 34 op-amp

topologies on amplication stages and evaluating the topologies through sizing. In this paper, we present the functional

block composition of several thousand op-amp variants, building up the amplication stages by their subblocks, starting

on transistor level with basic one-transistor functional blocks. New compared to [1], it presents:

•

An algorithm to synthesize every functional block of an op-amp by its functional subblocks starting on transistor

level up to whole op-amp topology (Sec. 3).

•An algorithm to synthesize a functional block based bias circuit for an op-amp topology (Sec. 4).

•An structural synthesis algorithm for op-amps featuring thousands of variations (Sec. 5 and Sec. 6).

•Experimental results (Sec. 7) featuring three op-amp types: single-output, fully-dierential, complementary.

•An outlook how this method can be extended to three-stage op-amp topologies (Sec. 8).

With the enhanced version of the synthesis method, up to 3912 op-amps can now be synthesized. The number of created

op-amps depends on the type of specication. Broad specications result in many synthesized topology alternatives,

while strict specications lead to a small set of synthesized netlists.

Manuscript submitted to ACM

FUBOCO: Structure Synthesis of Basic Op-Amps by FUnctional BlOck COmposition 3

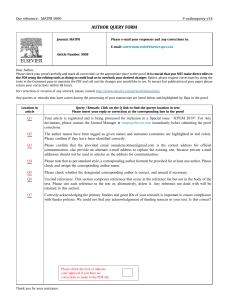

HL 5 Op-amps single-output (SO), fully-dierential (FD), complementary (Comp)

HL 4 Op-amp subblocks op-amp bias (𝑏𝑂), amplication stage (𝑎)

HL 3 Amplication stage subblock load (𝑙), transconductance (𝑡𝑐), stage bias (𝑏𝑠)

HL 2 Structures voltage bias (𝑣𝑏), current bias (𝑐𝑏), dierential pair (𝑑𝑝),

HL 1 Devices normal transistor (𝑛𝑡), diode transistor (𝑑𝑡 ), capacitor (𝑐𝑎𝑝)

Fig. 1. Hierarchical structure of functional blocks in op-amps

The goal of this approach is to perform op-amp synthesis using a formalized, computer-oriented description of

the fundamentals of op-amp design. The hierarchical structure of the approach allows a straightforward extension

to further functional blocks and multi-stage op-amp architectures. This allows not only to create suitable op-amps

for given specications sets, but also to create large circuit libraries containing only practicable solutions. Hence, the

created libraries provide large data sets for future machine learning projects.

In the following, an overview of the functional blocks in op-amps is given (Sec. 2). Sec. 3 describes the generic

algorithm to synthesis each functional block in Sec. 2 based on its subblocks. Sec. 4 describes the synthesis of the op-amp

bias circuit. Sec. 5 describes the creation of whole op-amp topologies based on the previous described algorithms. The

whole FUBOCO synthesis process is presented in Sec. 6. Experimental results featuring three op-amp types are presented

in Sec. 7. Sec. 8 discusses the extension of the method to three-stage op-amps. The paper ends with a conclusion (Sec. 9).

2 FUNCTIONAL BLOCKS IN OP-AMPS

Every op-amp consists of a set of transistor blocks which can be characterized by their function and are therefore

called functional blocks in the following. This paper presents a hierarchical structuring of these functional blocks and a

computer-oriented representation of the fundamental principles of op-amp design composition as described in standard

works [

8

,

13

,

18

,

26

,

27

,

29

]. An overview of the basic functional blocks structured on ve hierarchical levels is given

in Fig. 1. Examples are shown using four dierent op-amp topologies in Fig. 2. A more detailed description is given in

[2].

Hierarchy level 1 (HL 1) consists of devices, e.g., capacitors cap and transistors. Transistors are further divided into

groups according to their self-connection. Normal transistors (

𝑛𝑡

) are transistors without any self-connection, e.g., Fig.

2a, 𝑃1.Diode transistors (𝑑𝑡) are transistors with their gates connected to their drains, e.g., Fig. 2a 𝑃14.

Hierarchy level 2 (HL 2) consists of transistor structures, e.g., voltage bias (

𝑣𝑏

, Fig. 2a

𝑣𝑏𝐵𝑖𝑎𝑠 , 𝑣𝑏𝐷𝑖𝑠

), current bias (

𝑐𝑏

,

Fig. 2a

𝑐𝑏𝑛𝑇=1

) and dierential pair (

𝑑𝑝

, Fig. 2b

𝑁1, 𝑁2

). The voltage and current biases can be simple, e.g. Fig. 2a

𝑣𝑏𝑛𝑇=1

,

or cascode (Fig. 2d 𝑣𝑏𝐷𝑖𝑠 ).

Hierarchy level 3 (HL 3) consists of the amplication stage subblocks which are the transconductance (

𝑡𝑐

, Fig. 2, red),

the in-stage load (

𝑙

, Fig. 2, light green) and the stage bias (

𝑏𝑠

, Fig. 2, violet). In the following, we abbreviate the in-stage

load to load. For the transconductance, two main types exist: non-inverting (

𝑡𝑐𝑛𝑖𝑛𝑣

, Fig. 2b

𝑡𝑐𝑠

) and inverting (

𝑡𝑐𝑖𝑛𝑣

,

Fig. 2b). The non-inverting transconductance can be further divided into three types: simple (

𝑡𝑐𝑠

, Fig. 2b), complementary

(

𝑡𝑐𝑐

, Fig. 2c), and common-mode feedback (CMFB) (

𝑡𝑐𝐶 𝑀𝐹 𝐵

, Fig. 2a). The load consists of one or two load parts (

𝑙𝑝

,

Fig. 2, dark green).

Hierarchy level 4 (HL 4) consists of op-amp subblocks, which are the amplication stages (

𝑎

), and the op-amp bias (

𝑏𝑂

).

Two types of amplication stages exist: non-inverting (

𝑎𝑛𝑖𝑛𝑣

, Fig. 2a

𝑎𝑓 𝑐

), and inverting (

𝑎𝑖𝑛𝑣

, Fig. 2b). The non-inverting

amplication stages are further divided into simple rst stage (

𝑎𝑠

), complementary rst stage (

𝑎𝑐

, Fig. 2c), telescopic

Manuscript submitted to ACM

4 Inga Abel and Helmut Graeb

Bias

VDD

In+

In-

Vref

Out- Out+

, }

Op-amp core

(a) Folded-cascode op-amp with common mode feedback (CMFB)

(Fully-dierential, one-stage)

Op-amp core

Normal

Diode Transistor

Capacitor

Voltage

Current

Differential Pair

Load Parts

Load

Non

Inverting

Stage

Bias

First Stage

Second Stage

FeedbackStage

(b) Symmetrical op-amp with cascode sec-

ond stage (Single-output, symmetrical)

Op-amp core

(c) Complementary op-amp (One-stage)

Op-amp core

(d) Three-stage op-amp (Outlook, Sec. 8)

Fig. 2. Example topologies synthesizable with the presented method, colored background: functional blocks of HL 2 - 4

rst stage (

𝑎𝑡𝑒𝑙

), folded-cascode rst stage (

𝑎𝑓 𝑐

, Fig. 2a), symmetrical rst stage (

𝑎𝑠𝑦𝑚

, Fig. 2b) and common-mode

feedback stage (𝑎𝐶 𝑀𝐹 𝐵 , Fig. 2a).

Hierarchy level 5 (HL 5) consists of the op-amp itself. Three types of op-amps are subject of this paper: single-output

(SO), fully-dierential (FD) and complementary (Comp). Complementary op-amps are dened as op-amps having a

pmos and nmos dierential pair forming the input stage.

In the following, we will distinguish between the

𝑐𝑜𝑟𝑒

of an op-amp, containing the amplication stages and the

capacitors, and the op-amp bias

𝑏𝑂

, containing all transistors needed to bias the structures in the op-amp core (Fig. 2).

3 SYNTHESIS OF FUNCTIONAL BLOCKS EXCEPT OP-AMP BIAS

The hierarchical structure of functional blocks allows the synthesis of structural implementations of a functional bock

based on its subblocks. This section presents a new generic algorithm which covers all blocks in Fig. 1 except the

op-amp bias 𝑏𝑂. A separate algorithm to synthesize the op-amp bias is presented in Sec. 4.

3.1 Data Structure

A generic approach to synthesis of op-amp functional blocks requires the transition from a functional, i.e., behavioral,

description of a block, to a transistor implementation, i.e., to a structural description, of a block. In this transition, dierent

and new pins may arise. In this work, this transistion is implemented by representing functional blocks as instances

with specic sets of pins. The set of pins varies for dierent functional block (implementation) types. Each functional

block type has its own specic set of pins. The functional block voltage bias for instance has two implementation

Manuscript submitted to ACM

FUBOCO: Structure Synthesis of Basic Op-Amps by FUnctional BlOck COmposition 5

Diode

Transistor (dt)

𝑖𝑛

𝑠𝑜𝑢𝑟𝑐𝑒

𝑜𝑢𝑡1

Normal

Transistor (nt)

𝑖𝑛

𝑠𝑜𝑢𝑟𝑐𝑒

𝑜𝑢𝑡1

Diode Pair

(dip)

𝑖𝑛

𝑠𝑜𝑢𝑟𝑐𝑒

𝑖𝑛𝑛𝑒𝑟

𝑜𝑢𝑡1

𝑜𝑢𝑡2

Mixed Pair 1

(mp1)

𝑖𝑛

𝑠𝑜𝑢𝑟𝑐𝑒

𝑖𝑛𝑛𝑒𝑟

𝑜𝑢𝑡1

𝑜𝑢𝑡2

Voltage

Reference 1 (vr1)

𝑖𝑛

𝑠𝑜𝑢𝑟𝑐𝑒

𝑖𝑛𝑛𝑒𝑟

𝑜𝑢𝑡1

𝑜𝑢𝑡2

Voltage

Reference 2 (vr2)

𝑖𝑛

𝑠𝑜𝑢𝑟𝑐𝑒

𝑖𝑛𝑛𝑒𝑟

𝑜𝑢𝑡1

𝑜𝑢𝑡2

𝑖𝑛𝑛𝑒𝑟

vb

𝑖𝑛

𝑠𝑜𝑢𝑟𝑐𝑒

𝑜𝑢𝑡1

𝑜𝑢𝑡2

Fig. 3. Voltage bias instance and corresponding structural implementations

𝑆1, . . . , 𝑆𝑖: Structural implementation sets of FB1, . . ., FB𝑖(2, . . . , 𝑖 optional)

𝑅𝑐(optional): Characteristic connections of FB𝑛𝑒𝑤

R𝑓(optional): Rules 𝑠𝑛𝑒𝑤 must fulll

𝑅𝑎(optional): Additional connections 𝑠𝑛𝑒𝑤 can have

𝑃FB𝑛𝑒𝑤 : Pin set of 𝑠𝑛𝑒𝑤

Fig. 4. Input of Algorithm 1, FB𝑗:𝑗th functional block, 𝑠𝑗: a structural implementation of FB𝑗

types, i.e., simple and cascode (Fig. 3). If the voltage bias is simple, its instance has three pins:

𝑖𝑛, 𝑜𝑢𝑡1, 𝑠𝑜𝑢𝑟𝑐𝑒

. If the

voltage bias is cascode, its instance has two additional pins:

𝑖𝑛𝑛𝑒𝑟 , 𝑜𝑢𝑡2

. The pins dene the generic pin sets for the

two implementation types. They cover all possible implementation sets, even if an implementation as for instance vr1

happens to connect two pins. This data structure provides exchangeability and exibility in the synthesis process.

3.2 Generic Algorithm to Synthesize a Functional Block (Except Op-Amp Bias)

Alg. 1 creates for every functional block FB

𝑛𝑒𝑤

in Fig. 1 (but the op-amp bias) a set of structural implementations

(instances) 𝑆𝑛𝑒𝑤 .

3.2.1 Input. The input of the algorithm is dened in Fig. 4 and comprises the following sets.

Structural implementations

𝑆1, 𝑆2, .., 𝑆𝑖

of the functional subblocks of FB

𝑛𝑒𝑤

:

𝑖

is the number of functional subblocks

that are combined to build FB

𝑛𝑒𝑤

. E.g., a cascode voltage bias in Fig. 3 consists of two functional blocks, hence there

are two sets

𝑆1

,

𝑆2

. Each set consists of normal and diode transistors

𝑛𝑡 ∈𝑁𝑇 , 𝑑𝑡 ∈𝐷𝑇

having the same doping

Φ

(

𝑆1

:

𝑁𝑇Φ, 𝐷𝑇Φ

;

𝑆2

:

𝑁𝑇Φ, 𝐷𝑇Φ

;). Further input denes which combinations of these are allowed in a cascode voltage

bias.

Characteristic connections

𝑅𝑐

state how the instances in

𝑆1, .., 𝑆𝑖

are connected to each other. This input is optional as

no characteristic connections are provided for functional blocks consisting of one instance, e.g., simple voltage bias. To

create a cascode voltage bias,

𝑅𝑐

contains that the drain of a transistor

𝑠1∈𝑆1

must be connected to the source of a

transistor 𝑠2∈𝑆2(𝑅𝑐:𝑠1.𝑑𝑟𝑎𝑖𝑛 ↔𝑠2.𝑠𝑜𝑢𝑟𝑐𝑒).

Functional block rules

R𝑓

dene wanted and unwanted connections independent of the characteristic connections.

This is used to verify that a combination of dierent instances of functional subblocks is an implementation of FB

𝑛𝑒𝑤

.

E.g.,

R𝑓

of a cascode voltage bias (Fig. 3) contains that the pin

𝑖𝑛

, i.e.,

𝑠2.𝑑𝑟𝑎𝑖𝑛

, must be connected to one of the gates of

its subblocks (R𝑓:𝑠2.𝑑𝑟𝑎𝑖𝑛 ↔ (𝑠1.𝑔𝑎𝑡𝑒 ∨𝑠2.𝑔𝑎𝑡𝑒)).

Manuscript submitted to ACM

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

1

/

24

100%