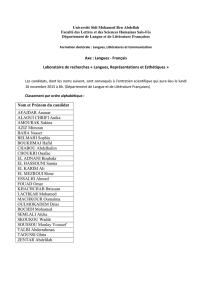

Université Mohammed V de Rabat

Ecole Supérieure de Technologie de Salé

Professeur Mohamed SBIHI

Automatismes Logiques

Circuits Numériques

Prof. Mohamed Sbihi

Université Mohammed V de Rabat

Ecole Supérieure de Technologie de Salé

Professeur Mohamed SBIHI

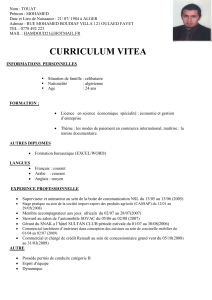

TABLE DES MATIERES

INTRODUCTION A L’AUTOMATISME ET AUX CONCEPTS

NUMERIQUES

A- INTRODUCTION A L’AUTOMATISME.…………...…………...………..5

I- Définition……….………………………………………………………….…5

II- Structure d’un système automatisé……………….……………….…….……5

III- Objectifs de l'automatisation…………………...………………………………6

III-1- Généralités ;…………..………...…………………………………………6

III-2- Objectifs de l’automatisation……..……………………………………….7

III-2- 1- Compétitivité du produit……………...………………….……………..7

III-2- 2- Exploitation de la machine de production…...……………..……….….8

IV- Cahier des charges d’un automatisme …………………..…………………..8

V- Technologie de la commande des systèmes automatisés……….....…………9

B- QUANTITÉS NUMÉRIQUES ET ANALOGIQUES……………………9

C- PRINCIPALES CATEGORIES DE SYSTEMES AUTOMATISES……13

CHAPITRE 1 : SYSTEMES DE NUMERATION -

ARITHMETIQUE BINAIRE - CODES

I- Systèmes de numération……………………………...…………………….....14

I-1- Système décimal…………………………….………………………………14

I-2- Système binaire…………………………….……………………………….15

II- Changement de base…………………….……………………………………16

II-1- Nombres entiers positifs…………………….……………...…………………16

II-2- Nombres fractionnaires…………………….……………..……… .………18

III- Nombres à virgule flottante………………….…………...………...……….19

IV- Arithmétique binaire……………………………………..……….………..21

IV- 1- Addition binaire………………………………………………....……….21

1

Université Mohammed V de Rabat

Ecole Supérieure de Technologie de Salé

Professeur Mohamed SBIHI

IV- 2- Ecriture des nombres signés……………………….…….………………...22

IV- 3- Notation en complément à 1……………………….……….…………..23

IV- 4- Notation en complément à 2……………………….……….…………..23

IV-5- Addition en utilisant le complément à 2………………..…………….…24

V- Les principaux codes……………………….…………..…………….……..25

V-1- Code binaire pur …………………………………….………….………..26

V-2- Code binaire décimal (DCB)………………………..………….…….…..26

V-2-1- Généralités……………………………………..………………..…..….26

V-2-2- Principaux codes binaires décimaux……………………..……..…...…27

V-3- Code Gray……………………………………………..………..…..…….30

V-4- Détection d’erreur au moyen de la méthode de parité………......………..31

V-5- Code ASCII : American standard code for Information Interchange….....32

CHAPITRE 2 : ELEMENTS D’ALGEBRE DE BOOLE

I- Règles générales de l’algèbre de Boole…..…………………….……............33

I- 1- Postulats de l’algèbre de Boole……………………………..…….………33

I- 2- Axiomes de l’algèbre de Boole…………………………..……….………34

I- 3- Conséquences directes des axiomes……………….………..…….………34

II – Les fonctions logiques………………………………………...………..….35

II- 1- Définition…………………………………………..…………….………35

II- 2- Table de vérité……………………………………………...………….…35

II- 3- Théorème de De Morgan…………………………………..…….…...….36

II- 4- Formes canoniques………………………………………...……………..37

II-4-1- Première forme canonique……………………………...………....……37

II-4-2- Deuxième forme canonique……………………………..……….……..38

II- 5- Les fonctions logiques à une seule variable binaire…….…………….….38

II- 6- Les fonctions logiques à deux variables binaires…………...……………41

II-7- Chronogramme d’une fonction……………………………………….......…46

2

Université Mohammed V de Rabat

Ecole Supérieure de Technologie de Salé

Professeur Mohamed SBIHI

CHAPITRE 3 : SIMPLIFICATION DES FONCTIONS LOGIQUES

I- Méthodes algébriques……………………………………….……………….47

II- Méthodes graphiques……….…………………………….…………………48

II-1- Tables de Karnaugh…………………………………......…..………….....48

II-2- Exemples……………………………………..…………...……..………..50

CHAPITRE 4 : SYNTHESE DES CIRCUITS COMBINATOIRES

I- Additionneur de base………………………………..……………………….54

I-1- Demi-additionneur……………………………..…………………………..54

I-2- Additionneur complet………………………………...……………………54

II- Additionneurs binaires parallèles………..…………….……………………56

III- Comparateur……………………………………………………….………58

IV- Décodeurs……………………………………...………………….……….62

V- Codeurs………………………………………...…………………..………66

VI- Multiplexeurs………………………………………………………………68

VII- Démultiplexeurs…………………………….………………….…………70

VIII- Unité arithmétique et logique (UAL)……………………...……………..71

INTRODUCTION A LA LOGIQUE SEQUENTIELLE ……………………… 73

CHAPITRE 5 : LES BASCULES

I- La bascule élémentaire R S……………………………………..………………76

II- Bascules synchrones……………………………………….………………..78

II- 1- Bascule RS synchrone ou RSH………………………….…………….…78

II- 2- Bascule D…………………………………………………….……………..79

II- 2- 1- La mémoire de donnée D Latch…………….…..……………………..79

II- 2- 2- Bascule D (edge triggered)………………….…...……………………80

3

Université Mohammed V de Rabat

Ecole Supérieure de Technologie de Salé

Professeur Mohamed SBIHI

II- 3- La bascule JK……………………………………….…………..……..…81

II-4- Bascule T…………………………………………………………...……..…83

II-5- Bascule RSH maître-esclave……………………………..………........….84

CHAPITRE 6 : LES COMPTEURS

I- Définitions– Généralités………………..……………………………………86

II- Les compteurs asynchrones…..………...….………………………………..86

II-1- Les compteurs modulo 2N asynchrones………...………………….………...86

II-1-1- Diviseur par deux ………………………………...….……….………...87

II-1-2- Réalisation d’un compteur asynchrone modulo 2N …………………...….87

II-1-3- Décompteurs asynchrones………………………………………..…….89

II.2. Compteur asynchrone modulo N < 2n (à cycle régulier)………...…………..89

III- Les compteurs synchrones………..………………………………...……...91

III-1- Les compteurs modulo 2N synchrone……………………………..………..91

III-2- Compteur synchrone modulo N < 2n (à cycle régulier)………...…………..93

IV- Exemple de CI………………………………………………….………..…94

CHAPITRE 7 : REGISTRES A DECALAGE

I- Fonction de base du registre à décalage…...………………………….……..95

II- Registres à décalage de type entrée série / sortie série…………....… .…….95

III- Registres à décalage de type entrée série / sorties parallèles…...…… .……..…96

IV- Registres à décalage de type entrées parallèles / sortie série……………… ..…97

V- Registres à décalage de type entrées parallèles / sorties parallèles..….. …..…..99

VI- Registres à décalage bidirectionnel………………………………….………..100

CHAPITRE 8 : EXEMPLES D’AUTOMATISME PAR CIRCUITS

NUMERIQUES… .……………………………………………………………….102

BIBLIOGRAPHIE………………………………………………………………..108

4

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

1

/

109

100%