FASCICULE DE TD

L’APPRENTIT BINAIRE {0,1}

1

LA LOGIQUE SEQUENTIELLE

1 -TRAVAUX DIRIGES

EXERCICES 1 : QUESTIONS DE COURS

1-c’est quoi un élément mémoire dans la logique séquentielle et quelle est son utilité ?

Un élément mémoire ou encore élément de mémorisation élémentaire permet de mémoriser l’état logique

d’un circuit séquentiel.

2-C’est quoi une horloge en logique séquentielle?

Une horloge est une variable logique qui passe successivement de 0 à 1 et de 1 à 0 d’une façon

périodique.

3-Quels sont les Avantages d’une Horloge ?

-Lire les valeurs qu’a des instants précis et à des intervalles reguliers ( ainsi elle n’est pas dans un

état valide en permanence) , l’instants est donnée par l’horloge.

- Permet de savoir quand est ce que l’on passe de t à t+1 .

4-Qu’est-ce que une Transition en logique séquentielle ?

-Une Transition est phénomène rencontre en logique séquentielle qui à un laps de temps Dt on a

changement du niveau logique des entrées permettant le changement d’état de la bascule (ou verrou)

.

5-Qu’est-ce qu’une Impulsion en logique séquentielle ?

- Une Impulsion qu’elle que soit sa durée est un évènement (constitué d’au moins une transition) qui

conduit à une réponse . On parlera souvent d’impulsion d’horloge au (front montant ou front

descendant).

6-Qu’est-ce qu’une bistable en logique séquentielle ?

Un bistable représente deux états stables dans le temps.

FASCICULE DE TD

L’APPRENTIT BINAIRE {0,1}

2

7-Qu’est-ce qu’une bascule en logique séquentielle ?

Une bascule est un élément de base de la logique séquentielle composé de bistable pouvant prendre

deux états logiques 0 et 1 .

8-Qu’els sont les carateristiques d’une bascule logique séquentielle?

C’est composant sont faits de bistables (deux états stables ) .

-possibilité de passer d’un états à un autre.

-il peut gérer et changer l’état de plusieurs façons en fonction de ses dérivés ( types de bascules jk

, rs , t , d , …)

9-C’est quoi un système séquentielle dit synchrone ?

-Un système séquentielle synchrone est lorsque tout les changements d’états du système sont liées à

l’activité d’un meme signal d’horloge. t

10-C’est quoi un système séquentiel dit asynchrone ?

-Un système séquentielle asynchrone est lorsque le changement d’états du système sont liées au

changements des entrées.

11-Citez les différences entre un système séquentielle dit synchrone et un système séquentielle dit

asynchrone ?

-Un système séquentielle synchrone est lorsque tout les changements d’états du système sont liées à

l’activité d’un meme signal d’horloge alors que Un système séquentielle asynchrone est lorsque le

changement d’états du système sont liées au changements des entrées et ils ne possèdent pas ainsi

d’Horloges ( signal d’horloge ) .

- Dans un SSS les sorties sont récalculées en fonctio d’un signal d’horloge en entrée ( nécessite ainsi

une entrée de contrôle pour ce signal d’horloge ) alors que un SSAS les sorties sont récalculées à

chaque changement des valeurs en entrées.

12-C’est quoi la différence entre une ROM et un Système Séquentielle dans un point de vue de mémoire ?

La ROM ( Read Only Memory ) se comportait comme une mémoire adressable et donc est différent du

caractères Sequentiel de ces nouveaux éléments de mémoire compris dans un Système séquentielle et

renvoie au fait que le temps de consultation des données dans le circuit joue tout un rôle dans son

fonctionnement car pour parvenir à ce résultat, il faut jouer sur les délais de propagation des signaux dans

les portes logiques ou introduire une rétroaction.

13-Quelle est la Différence entre circuit combinatoire et un circuit séquentiel ?

FASCICULE DE TD

L’APPRENTIT BINAIRE {0,1}

3

Un circuit Combinatoire est un circuit (Numérique) logique dont les sorties dépendent uniquement des

entrées. S= f(t) , alors qu’un Circuit séquentielle est un circuit (Numérique) logique dont l’état à l’instant

t+1 est une fonction des éntrées à ce même instant (t+1) et de l’état précédent du système (instant t ).

S = f ( E , S )

t+1 t

14-Dégager= de la question numéro 13 la définition de circuit combinatoire et circuit Séquentielle ?

Juste impeu de bon sens .

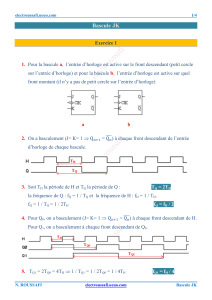

15-C’est quoi un Chronogramme ?

Un chronogramme est une représentation graphique de l’évolution temporelle d’un signal électrique ou

logique.

16- JOEL STEPHANE ne c’est pas distinguez correctement le notion de front montant & descendant

essayez par un schéma de résoudre son problème et d’apporter une remarque pertinente à cette notion.

16-1) schématisez pour une variable logique donnée s son front montant et descendant.

16-2) ressortez de ce schéma une remarque pertinante au Probleme de JOEL STEPHANE .

**correction **:

JOEL STEPHANE écoute tout d’abord un chrogramme est ( définition voir exercice 1 num 15 ) ; Alors on

trouve sur l’axe des abscisses le temps , sur l’axe des ordonnées l’état (0 ou 1 ) des variables étudiées. (Une

variable logique s est nécessaire tu vera pourquoi juste en dessous ) .

a*Schématisons tout cela avec notre variables logique ‘S’ :

Voila à quoi la petite phrase du haut se résume en terme de chronogramme mais c’est pas terminez :

JOEL STEPHANE écoute je vais t’expliquez illico presto la notion de front Pour cela , Une variable logique

s est nécessaire car elle peut avoir deux niveaux ; le niveau logique haut 1 (vrai) et le niveau logique bas 0

(faux). Quand elle passe du niveau bas vers le niveau haut, elle définit le front montant. Dans le cas

contraire, elle définie le front descendant.

b*Schématisons tout cela avec notre variables logique ‘S’ :

FASCICULE DE TD

L’APPRENTIT BINAIRE {0,1}

4

16-2) Remarque

_ _ _

Le front montant ↑ 𝑎 correspond au front descendant de ↓ 𝑎 et vis-versa. ↑ a =↓ 𝑎 et ↓ 𝑎 = ↑ 𝑎 .

15-Quand dit-on qu’un Système Séquentielle est une machine de mealy ?

Si les valeurs des variables de sorties dépendent de l’etat présent et des variables d’entrées.

Bref le changement des sorties n’est pas synchrone : il se fait avec le changement des entrées.

16-Quelles sont les contraintes à imposer sur une machine séquentielle pour qu’elle soit réalisez sous la

forme d’un automate de Moore ?

*Lorsque les valeurs des variables de sorties dépendent uniquement de l’etat présent le Système

Séquentielle est une machine de Moore . (d’où il faudrait avoir cette containte ci ) ;

*Le changement ( des sorties ) est synchrone et se fait avec changement des Etats.

FASCICULE DE TD

L’APPRENTIT BINAIRE {0,1}

5

EXERCICES 3 :

A-Donnez la table de vérité , symbole de la bascules RS (asynchrone ) ,préciser ca structure interne à

l’aide de la porte nor .

B-Donnez la table de vérité , symbole de la bascules RS (asynchrone ) ,préciser ca structure interne à

l’aide de la porte nand . CORRECTION EXERCICE 3CORRECTION EXERCICE 3

C-Donnez la table de vérité et symbole de la bascules JK ( a déclenchement sur front ) ,préciser ca

structure interne a l’aide de la porte nand .

D-Donnez la table de vérité et symbole de la bascules D ( a déclenchement sur front ) ,préciser ca

structure interne a l’aide de la porte nand .

E-Donnez la table de vérité et symbole de la bascules T ( a déclenchement sur front ) ,préciser ca

structure interne a l’aide de la porte nand .

EXERCICES 4:

1-représentez la bascule D flip-flop à déclenchement sur front montant avec clear

et preset actifs à 0 ( précisez sa table de transition ainsi son symbole ).

2-Expliquez brièvement sont fonctionnement .

EXERCICES 5:

1-Transformez une bascule JK en une bascule D.

2-Réaliser le circuit qui permet de réaliser le cycle suivant 0,1,2,3 à l’aide de bascule JK .

EXERCICES 6 : (savoir où l’on se trouve !!! )

Le circuit suivant est-il combinatoire ou séquentiel ? Pourquoi ?

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

1

/

26

100%