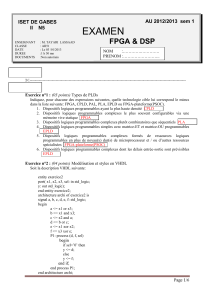

VHDL: Structures de base et synthèse d'opérateurs standards

Telechargé par

abdeslam lachhab

VHDL

Structures de bases

Synthèse d’opérateurs standards

2

Présentation

Electronique reprogrammable

Apparition des premiers circuits vers les années 70: premiers PLD-> PAL, GAL

Evolution vers composants plus complexes: CPLD, FPGA

Différentes technologies pour la programmation des connexions

Permanents , Volatiles statiques, Volatiles

Capacitéde programmation In-Situ

•composants dits ISP via interface JTAG

Contexte de compétitivitémondiale

Importance du

Time-To-Market

3

Connexions programmables

Introduction

Deux formes canoniques pour les équations logiques

Somme de produits S=a.b+ c.d

Produits de somme S=(z+f).(e +x)

Connexions programmables

ET cablé

OU cablé

Constitution d’un réseau

programmable

Représentation

standard

4

xPLD

Simple Programme Logic Device

Composants simples

réseau ET/OU programmable ou fixe

PAL (OTP en général), GAL reprogrammable

Différentes familles en

fonction des ressources

rajoutés par le constructeurs

5

FPGA

Field Programmable Grid Array

Granularitéplus fine que les CPLD ( macrocellules - complexes mais + nombreuses)

Intégration matérielle de composants supplémentaires

RAM: appeléLUT (Look-Up Table)

Mutiplexeurs divers

PLL

Multiplieurs câblés (FPGA haut de gamme => concurrence avec les DSP)

Réseau de routage réparti ( non centralisécontrairement aux CPLD)

Exemple de référence

Famille Cyclone (FPGA Low Cost

d’ALTERA)

Concurrent: Spartan3 (chez Xilinx)

Répartition des applications

Source Altera

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

1

/

45

100%