PLAN DU CHAPITRE III

Introduction

Définition d’une interruption

Déroulement d’une routine d’interruption

Types d’interruptions

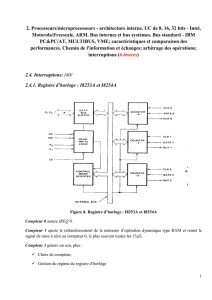

Registre d’interruption

Détection d’une interruption

Contexte du processus

Recherche de la cause d’une interruption

Systèmes d’interruptions hiérarchisées

Système des interruptions du 8086

2

3

Sur une machine monoprocesseur, un seul programme (ou

processus) est exécuté à la fois.

Une autre composante peut demander à l’interrompre

pour faire temporairement autre chose. Par exemple:

Périphérique : un paquet réseau arrive, la souris a bougé

Gestion erreur : erreur arithmétique, instruction invalide

Il faut donc introduire un mécanisme matériel qui indique

au processeur d’arrêter le traitement courant. Ce

mécanisme s’appelle une interruption.

INTRODUCTION

4

Une interruption est un mécanisme qui permet d'interrompre

l'exécution d'un processus suite à un événement extérieur ou intérieur

et de passer le contrôle à une routine dite "routine d'interruption"

ou traitement d’interruption.

Le système d'interruption est un dispositif, incorporé au niveau du

séquenceur, qui enregistre et traite les signaux d'interruption envoyés

au processeur :

1. Arrêter le processus en cours ;

2. Sauvegarder le contexte du processus interrompu;

3. Exécuter le programme de routine d'interruption ;

4. Restaurer le contexte du processus interrompu;

5. Reprendre l'exécution du processus interrompu.

DÉFINITION DE L’INTERRUPTION

5

Donc, lorsque l'interruption se produit le processeur, après la fin de l'exécution

de l'instruction en cours, transfère le contrôle à la routine d'interruption

associée à l'événement.

La routine d’interruption fait d’abord une sauvegarde du contexte du

processus interrompu avant de réaliser son traitement.

A la fin de celui-ci l, le contexte du processus interrompu est restauré ce qui

lui permet de continuer son exécution convenablement à l’endroit où il a été

interrompu.

DÉROULEMENT D’UNE ROUTINE D’INTERRUPTION

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

1

/

43

100%