Processeurs et Architectures Numériques (PAN)

PROCESSEURS ET ARCHITECTURES

NUMÉRIQUES (PAN)

PARTIE 1: SUPPORT DE COURS

ANNÉE 2014/2015

JEAN-LUC DANGER

GUILLAUME DUC

TARIK GRABA

YVES MATHIEU

ALEXIS POLTI

LAURENT SAUVAGE

TELECOM PARISTECH

Table des matières

1De la logique combinatoire à l’arithmétique 5

1.1La logique booléenne 5

1.2Fonctions logiques élémentaires 7

1.3Fonctions logiques importantes 10

1.4Représentation des nombres 14

1.5Opérateurs arithmétiques 18

1.6Du temps de propagation au temps de calcul 22

2La logique séquentielle 25

2.1Mémorisation et logique séquentielle 25

2.2Logique séquentielle synchrone 25

2.3La bascule D 27

2.4Généralisation 34

2.5Applications de la logique synchrone 35

3Le nano processeur 41

3.1Programme, instructions et données 41

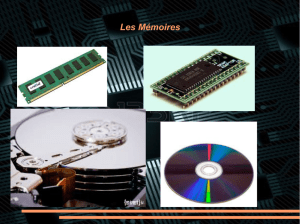

3.2La mémoire RAM 42

3.3Le système de base 44

3.4Première version du microprocesseur : l’automate linéaire 45

3.5Deuxième version du microprocesseur : l’automate avec accumulateur 50

3.6Troisième version du microprocesseur : l’automate avec accumulateur et indirection 54

3.7Quatrième version du microprocesseur : le processeur RISC 58

3.8Les périphériques 63

4

4La logique CMOS 65

4.1Construisons des fonctions logiques 65

4.2La logique CMOS 67

4.3Performances de la logique CMOS 69

4.4Évolutions technologiques et lois de Moore 73

A Annexe : SystemVerilog 81

A.1Quelques règles générales de syntaxe 81

A.2Les modules 81

A.3Contenu des modules : Structures et instanciation de modules 83

A.4Contenu des modules : Description d’un comportement combinatoire 84

A.5Contenu des modules : Description d’un comportement séquentiel synchrone 89

A.6Généralisation des processus always 91

A.7Codage des états des automates finis 92

1

De la logique combinatoire à l’arithmétique

Dans ce chapitre, nous allons introduire la notion de logique combinatoire en présentant les bases de la logique

booléenne (cf. section 1.1), puis les fonctions logiques élémentaires (cf. section 1.2) ainsi quelques fonctions plus

complexes mais souvent utilisées (cf. section 1.3). Nous verrons ensuite comment représenter des nombres (cf. sec-

tion 1.4) et comment réaliser des opérations sur ces nombres (cf. section 1.5). Enfin, nous introduirons le concept de

temps de propagation dans les opérateurs logiques (cf. section 1.6).

1.1La logique booléenne

1.1.1Introduction

Soit El’ensemble à deux éléments 0, 1.

Une variable logique est un élément de E. Elle ne possède donc que

deux états : 0 ou 1.

Une fonction logique est une application de E×E. . . ×Edans E

qui associe à un n-uplet de variables logiques (e0,e1, . . . , en), souvent

appelées entrées, une variable logique s=F(e0,e1, . . . , en), souvent

appelée sortie.

On distingue deux catégories de fonctions logiques, en fonction

de leur comportement temporel.

Une fonction combinatoire est une fonction logique pour laquelle la

sortie ne dépend que de l’état actuel des entrées :

∀t,s(t) = F(e0(t),e1(t), . . . , en(t))

Une fonction séquentielle est une fonction logique pour laquelle la

sortie dépend de l’état actuel de ses entrées mais également de leurs

états passés :

s(t) = F(e0(t),e1(t), . . . , en(t),e0(t−t1),e1(t−t1). . . )

Dans ce chapitre, nous ne traiterons que des fonctions combi-

natoires. Les fonctions séquentielles seront introduites dans le cha-

pitre 2.

1.1.2Représentation des fonctions logiques

Il existe plusieurs méthodes pour décrire une fonction logique

combinatoire. Ces méthodes sont toutes équivalentes et le choix de

l’une ou l’autre ne va dépendre que du contexte d’utilisation.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

1

/

94

100%