Les Mémoires - Le site de la SIN

Ecran

Carte mère

CPU

Mémoire vive ( RAM)

Cartes périphériques

Alimentation

Lecteur CD

Disque Dur

Souris

Clavier

µProcesseur

Chipset

Slots Mémoire

Port Vidéo

Port IDE ( disque dur )

Connecteur ATX ( Alimentation )

Ports SATA ( disque dur )

Connecteurs PCI ( extensions )

Connecteur Floppy ( disquette )

Connecteur boitier

!

Enre

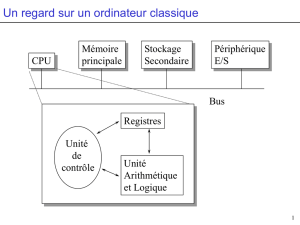

Central Process Unit*: effectue les calculs

Stocke les programmes et les données

Enregistre les résultats intermédiaires et finaux

En entrée*: Clavier, souris, disque dur...

En sortie*: Carte graphique, disque dur ….

Bus Système et communication avec le CPU

Bus AGP ou PCI*: Communication avec la carte graphique

Bus mémoire*: communication avec la mémoire

Bus PCI*: carte réseau, son ….

Bus de communication avec les périphériques de stockage ( DD, CD .. )*:

ATA, SATA, PCI

Connexion de périphériques extérieurs*: USB ….

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

1

/

30

100%

![Fonctionnement [modifier]](http://s1.studylibfr.com/store/data/005169927_1-0818c4796cfa4f2cca392c81b1fcd146-300x300.png)