Familles de CI

Classe: 1-SI FAMILLES DE CIRCUITS INTEGRES Durée : 1 h

1. PRINCIPALES FAMILLES DE CIRCUITS LOGIQUES :

F Technologie TTL (Transistor Transistor Logique).

•TTL standart : exemple 7408, 5408;

•TTL LS : Low Power Schottky : exemple 74LS00, 54LS00;

•TTL S: Schottky : exemple 74S08, 54S08;

•TTL ALS : Advenced Low Power Schottky : exemple 74ALS08, 54ALS08;

•TTL F : Fast : exemple 74F08, 54F08;

•TTL AS : Advenced schottky : exemple 74AS136

F Technologie CMOS (Complementary Mos).

•HC MOS : exemple 74HC540;

•HCT : exemple 74HCT573;

•ACL (AC / ACT);

•BiCMOS (BCT);

•Adevneced BiCMOS (ABT);

F Technologie ECL.

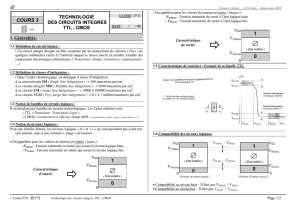

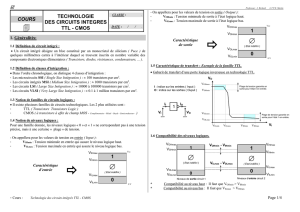

1-1. Repérage des circuits intégrés DIL (DUAL IN LINE) :

1-2. Conventions - Repérage des tensions et des courants :

On adopte la convention RÉCEPTEUR en entrée comme en sortie :

En entrée (Input) En sortie (Ouput)

IiL Courant d'entrée à l'état bas. IoL Courant de sortie à l'état bas.

IiH Courant d'entrée à l'état haut. IoH Courant de sortie à l'état haut.

ViL Tension d'entrée à l'état bas. VoL Tension de sortie à l'état bas.

ViH Tension d'entrée à l'état haut. VoH Tension de sortie à l'état haut.

1SI-FAMILLE DE CI.sxw Page - 1 / 9 - M.DEZEST-25/03/05

9 817 16 15 14 13 12 11 1018

2 3 4 5 6 7 8 91

L'ergot ou le point

permettent de

repérer la broche 1

Sens croissant des numéros des broches

CIRCUIT 18 broches en boîtier DIL

74 HCT 573

14 13 12 11 10

2 3 4 5 6 71

CIRCUIT 14 broches en boîtier DIL

74 LS 08

&Io

Ii

En entrée - Input : I En sortie - Ouput : O

Vi Vo

Les courants Ii et Io entrent par les

broches :

lIi = 40 µA : le courant réel entre bien

par la broche;

lIi = -1,6 ma : le courant réel sort de

la broche.

Classe: 1-SI FAMILLES DE CIRCUITS INTEGRES Durée : 1 h

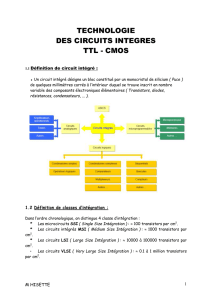

2. MARQUAGE DES CIRCUITS INTEGRES :

3. FAMILLES TTL : Elles utilises des transistors bipolaires : NPN ou PNP.

β = h21e = gain en courant dans le montage émetteur commun (relié à la masse).

3-1. TTL standard :

F Etage de sortie de type totem pole :

1SI-FAMILLE DE CI.sxw Page - 2 / 9 - M.DEZEST-25/03/05

SN

Code du

fabriquant :

Texas

Instrument

74

Plage de température

54 : usage militaire (-55°C à +125 °

C);

74 : usage commercial.

l 0 à 70 °C pour le bipolaire;

l -40°C à 85°C pour le CMOS

ACT

Famille technologique

16 245 NT

Identification fonction

N° Identifiant le circuit

Forme du boîtier

Ib

Ic

Ie

C : Collecteur

Base : B

E : Emetteur

Vce

Vbe

Vcb

Transistor NPN

Ib

Ic

Ie

C : Collecteur

Base : B

E : Emetteur

Vce

Vbe

Vcb

Transistor PNP

NPN

Ie = Ic + Ib

Ic = β x Ib

Ib > 0

Ic > 0

Ie > 0

Vce ≥ 0

Vbe > 0

Vcb > 0

Ie = Ic + Ib

Ic = β x Ib

Ib < 0

Ic < 0

Ie < 0

Vce ≤ 0

Vbe < 0

Vcb < 0

PNP

e1

e2

e3

4KΩ1,6

KΩ

Q3

Q2

Q1

Q4

100Ω

Vcc

Sortie

GND

Etage de sortie

de type Totem pole

1KΩ

D1

Les sorties totem pôle ne permettent

pas de réaliser un OU câblé.

Si on connecte deux sorties totem

pôle ensembles, les deux portes sont

détruites.

Q3

Q4

100Ω

Vcc

Porte 1

GND

D1

100Ω

Q3

D1

Q4

Porte 2

Classe: 1-SI FAMILLES DE CIRCUITS INTEGRES Durée : 1 h

F Etage de sortie de type Collecteur ouvert (Open collector) :

Avec des portes de type collecteur ouvert le OU câblé est possible.

F Etage de sortie de type 3 états (3 State Outputs) : une entrée de validation (EN) permet

de valider la sortie.

➢Exemple : 8 bascules D 74 HCT 573

1SI-FAMILLE DE CI.sxw Page - 3 / 9 - M.DEZEST-25/03/05

e1

e2

e3

4KΩ1,6

KΩ

Q2

Q1 Q3

Vcc

Sortie

GND

Etage de sortie

de type Collecteur ouvert

1KΩ

Vcc

Symbole d'une sortie

à collecteur ouvert

Vcc

R

D

e1 e2

e1

0

0

1

1

e2 D

0

1

0

1

e2

e1

D

D = ......................

Vcc

R

D

e1

e1Q2

Q4

Vcc

Sortie

GND

Etage de sortie

de type 3 Etats

=1

EN EN

Symbole d'une

sortie 3 Etats

1D (2) 1D 1Q

(19)

2D (3) 2Q

(18)

3D (4) 3Q

(17)

4D (5) 4Q

(16)

5D (6) 5Q

(15)

6D (7) 6Q

(14)

7D (8) 7Q

(13)

8D (9) 8Q

(12)

(11)

(1)

OC

C C1

EN

INPUTS

OUTPUTS

Q

ENABLE

OC C D

L H H

L H L

L K X

H X X

H

L

Qo

Z

Classe: 1-SI FAMILLES DE CIRCUITS INTEGRES Durée : 1 h

3-2.TTL Schottky :

Elle utilise des diodes rapides de type Schottky et des transistors bipolaires en quasi-

saturation. Cela augmente la rapidité.

F Exemple : porte NON-ET :

La technologie Schottky comprend entre autres les familles S, LS , AS et ALS

4. Famille C-MOS : (Complementary Métal Oxyde semiconductor).

Elle utilise des transistors MOS, pilotés en tension et se distingue par une très faible puissance

dissipée en statique.

On rencontre plusieurs types :

•74 HC XX : Haute vitesse CMOS;

•74 HCT XX : Haute vitesse CMOS compatible broche à broche avec la TTL.

•74 AC XX : Advanced CMOS.

•74 BCT XX :

•74 BCT xx:

•Série 4000 : On notera que la série 4000 peut être alimentée sous une tension

d’alimentation de 3 V à 18 V : (Voir documentation porte 4093).

1SI-FAMILLE DE CI.sxw Page - 4 / 9 - M.DEZEST-25/03/05

120Ω

4KΩ

8KΩ20KΩ

Sortie

e1

e2

e3 4KΩ4KΩ

Diode Schottky Transistor Schottky

Classe: 1-SI FAMILLES DE CIRCUITS INTEGRES Durée : 1 h

5. Famille ECL : (Emitteur Coupled Logic).

Elle utilise des transistors bipolaires à couplage d’émetteur. C’est la technologie la plus rapide

à l’heure actuelle.

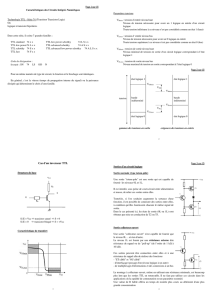

6. Caractéristiques générales des circuits logiques : niveaux logiques.

Les niveaux des tensions à l’état haut et bas sont différents en entrées et en sortie pour

garantir les niveaux logiques quand la sortie d’une porte pilote l’entrée d’une seconde porte.

F Exemple avec 2 portes TTL LS : les niveaux des tensions sont compatibles.

•La porte 2 voit bien un niveau logique 1 quand la sortie de la porte 1 est à l’état haut.

•De même qu’elle voit bien un niveau logique 0 quand la sortie de la porte 1 est à l’état bas.

Pour chaque famille de circuit logique, les constructeurs fournissent les différentes tensions

correspondantes aux niveaux logiques d’entrée et de sortie.

1SI-FAMILLE DE CI.sxw Page - 5 / 9 - M.DEZEST-25/03/05

MOS P

MOS N

Ve Vs

=1

12345

1

2

3

4

5

Ve(V)

Vs(V)

Vo

=1

Vi

Entrée Sortie

Niveau logique 0

Niveau logique 1

Entrée Sortie

VOHmin=2,4V

VILmin=2 V

VILmax=0,8 V

Niveau logique 0

VILmax=0,4 V

Niveau logique 1

Vo

=1

Vi

Porte 1 : TTL LS Porte 2 : TTL LS

=1

6

6

7

7

8

8

9

9

1

/

9

100%