Diapositive 1

A. Objectifs de la séquence:

à l'issue de la séquence, il faut être capable de:

•Lire les fiches techniques des constructeurs

•Comparer les caractéristiques des différentes familles TTL.

•Déterminer la sortance d’un dispositif logique

•Exploiter les éléments logiques à collecteur ouvert..

•Différencier les principaux caractères des différentes

familles logique TTL CMOS

B) Généralités

•B.1)évolution de la technologie

1.Logique câblée à éléments discrêts

+V

b

aa.b

Les premiers circuits logiques étaient constitués de composants discrets

(résistances,diodes,transistor,capacités,Zener) câblés sur cartes puis sur

circuits imprimés.

a)Logique à diode

-Les niveaux logiques se dégénèrent lors du passage d'une porte.

-Forte consommation

b)Logique à éléments actifs.

L'utilisation d'un élément actif (transistor) permet de régénérer les niveaux

logiques à chaque porte.

Logique TTL: Les circuits d'entrée et de sortie sont réalisés avec des

transistors.

2. Logique intégré

L'intégration à permis une miniaturisation et une

augmentation des performances des circuits logiques.

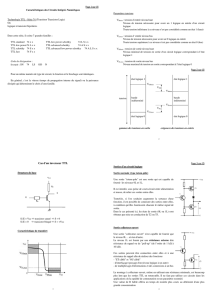

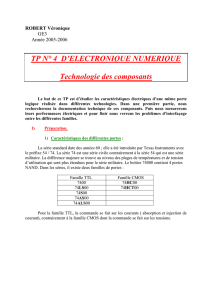

Technologie CMOS

Technologie TTL

Tableau comparatif entre la technologie bipolaire et

CMOS

Bipolaire TTL CMOS

Tension d'alimentation stricte à 5V

Immunité au bruit inférieure à celle

du CMOS

•Plus de courant transitant

Basse impédance d'entrée

Possibilité de laisser les entrées

inutilisées en l'air

Utilisation décroissante.

Tension d'alimentation comprise entre

3 et 18V

Immunité au bruit > au TTL

pas de courant

Forte impédance d'entrée

obligation de polariser les entrées

en l'air

Préférence des concepteurs

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

1

/

19

100%