technologie des circuits integres ttl - cmos - Sn-Bretagne

M HISETTE

1

TECHNOLOGIE

DES CIRCUITS INTEGRES

TTL - CMOS

1.1 Définition de circuit intégré :

▪ Un circuit intégré désigne un bloc constitué par un monocristal de silicium ( Puce )

de quelques millimètres carrés à l’intérieur duquel se trouve inscrit en nombre

variable des composants électroniques élémentaires ( Transistors, diodes,

résistances, condensateurs, ... ).

1.2 Définition de classes d’intégration :

Dans l’ordre chronologique, on distingue 4 classe d’intégration :

* Les microcircuits SSI ( Single Size Intégration ) : 100 transistors par cm2.

* Les circuits intégrés MSI ( Médium Size Intégration ) : 1000 transistors par

cm2.

* Les circuits LSI ( Large Size Intégration ) : 10000 à 100000 transistors par

cm2.

* Les circuits VLSI ( Very Large Size Intégration ) : 0.1 à 1 million transistors

par cm2.

M HISETTE

2

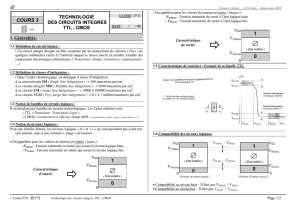

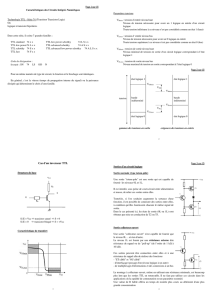

1.3 Notion de niveaux logiques :

Pour une famille donnée, les niveaux logiques « 0 » et « 1 » ne correspondent pas à une tension

précise, mais à une certaine « plage » de tension.

On appellera pour les valeurs de tension en entrée ( Input ):

* VIHmin : Tension minimale en entrée qui assure le niveau logique haut.

* VILmax : Tension maximale en entrée qui assure le niveau logique bas.

On appellera pour les valeurs de tension en sortie ( Output ):

* VOHmin : Tension minimale de sortie à l’état logique haut.

* V0Lmax : Tension maximale de sortie à l’état logique bas.

1.4 Compatibilité des niveaux logiques.

* Compatibilité au niveau haut : Il faut que VOHmin > VIHmin

* Compatibilité au niveau bas : Il faut que VILmax > VOlmax

Caractéristique

d’entrée

1

0

( Etat indéfini )

Vcc

VIHmin

VILmax

1

0

( Etat indéfini )

Vcc

1

0

VIHmin

( Etat indéfini )

VILmax

Vcc

Caractéristique

de sortie

VOHmin

VOLmax

0

VOHmin - VIHmin

1

0

( Etat indéfini )

Vcc

VOHmin

VILmax - VOLmax

VOLmax

Niveaux d’entrée circuit 2

Niveaux de sortie circuit 1

0

0

M HISETTE

3

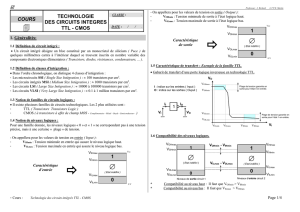

1.5 Temps moyen de propagation.

Lorsqu’on applique à l’entrée d’un circuit un niveau logique, il y a un certain retard pour que la

sortie réagisse. Cette durée est le temps moyen de propagation tPD.

* tPHL: Temps de propagation du niveau haut au niveau bas.

* tPLH: Temps de propagation du niveau bas au niveau haut.

Remarque : Ce temps détermine la fréquence maximale FMAX à laquelle les circuits intégrés sont

capables de réagir.

1.6 Facteur de charge : Sortance N.

Ce paramètre caractérise le nombre N maximal d’entrées de portes logiques pouvant être

commandées par la sortie d’un autre opérateur logique de la même famille.

* Sortance N ( A l’état haut ) = IOH / IIH

* Sortance N ( A l’état bas ) = IOL / IIL

Remarque : La documentation constructeur fournie les données suivantes : IOH, IIH, IOL, IIL.

1.7 Notion de familles de circuits logiques :

Il existe plusieurs familles de circuits technologiques. Les 2 plus utilisées sont :

* TTL ( Transistors Transistors Logic )

* CMOS (transistors à effet de champ MOS - Complémentaire - Métal - Oxyde - Semiconducteur - )

IO

S

tPLH

tPHL

Entrée

Sortie

50%

t

tPD = (tPHL + tPLH ) / 2

X

X

X

X

II

II

II

IOH : Courant de sortie maximal à l’état haut

IOL : Courant de sortie maximal à l’état bas

IIH : Courant d’entrée maximal à l’état haut

IIL : Courant d’entrée maximal à l’état bas

M HISETTE

4

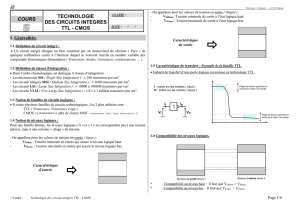

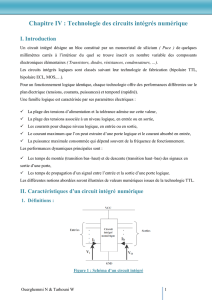

Niveaux Logiques d ’une porte logique TTL (LS)

Plusieurs technologies :

TTL standard (n ’est plus utilisée) 74 00

TTL Low Power 74 L 00

TTL Schottky (Rapide) 74 S 00

TTL Low Power Schottky 74 LS 00

TTL Advanced Schottky 74 AS 00

TTL Advanced Low Power Schottky 74 ALS00

Caractéristiques de fonctionnement :

Gamme d’alimentation : 5 V +/- 5%.

Gamme de température : de 0 °C à + 70 °C.

Puissance dissipée : environ 2 mW par porte (série

LS).

Fréquence de fonctionnement : jusqu’à 3 MHz.

Sortance : jusqu’à 20 (série LS).

(Nombre d’entrées que l’on peut relier à une sortie de porte)

Faible immunité aux bruits.

Caractéristique d ’Entrée/Sortie d’un inverseur

PORTES LOGIQUES TTL Transistor Transistor Logique

Fiche de référence

N°7

V

O

V

I

VCC

VOH

0

VCC

VOL

VIL

VIH

&

74 LS

00

V

I

V

O

ENTREE

SORTIE

V

O

VOH mini

VOL maxi

VCC

0 V

0,5 V

2,7 V

5 V

Niveau ‘ 0 ’

Niveau ‘ 1 ’

Niveau

indéterminé

V

I

VIH mini

VIL maxi

VCC

0 V

0,7 V

2 V

5 V

Niveau ‘ 0 ’

Niveau ‘ 1 ’

Niveau

indéterminé

Sortie à collecteur ouvert (Open collector

output)

Sortie 3 états (3-state

output)

Symbole

Symbole

V

O

To

On sort directement sur le

collecteur du transistor de

sortie.

Obligation de connecter

une résistance R de tirage au

+5 V.

Pour un calcul rigoureux de R,

se reporter à la page 43 du

Memotech

V

O

La sortie est

équivalente

à un

interrupteur.

V

O

T1

T2

+5V

Dans une porte classique, l ’un des 2 transistors T1 ou T2 du totem pôle est

conducteur.

Dans une porte 3 états, il est possible de bloquer simultanément les 2 transistors T1

et T2 par l ’entrée de validation EN (EN = 0).

On dispose alors de 3 états en sortie:

EN T1 T2 Etat

1 Passant Bloqué Haut

1 Bloqué Passant Bas

0 Bloqué Bloqué Haute impédance (Sortie ‘ en l ’air ’).

M HISETTE

5

Rs

RG

VDD

VOH

IOH

RS

VOL

IOL

CG

VIH

IIN

RG

CG

VIL

IIN

ENTREE

SORTIE

Modélisation de l’entrée et de la sortie d’une porte logique CMOS

Etat logique ‘ 1 ’

Etat logique ‘ 1 ’

Etat logique ‘ 0 ’

Etat logique ‘ 0 ’

GRANDEURS

CARACTERISTIQUES :

VOH : Tension de sortie à l ’état haut.

VOL : Tension de sortie à l ’état bas.

VIH : Tension d ’entrée à l ’état haut.

VIL : Tension d ’entrée à l ’état bas.

IOH : Courant de sortie à l ’état haut.

IOL : Courant de sortie à l ’état bas.

IIN : Courant d ’entrée.

RS = environ 300

RG = plusieurs M

CG = environ 50 pF

V

O

V

I

VDD

VDD

VDD / 2

0

Plusieurs technologies :

Série 4000 :

40 00 B (sorties bufférisées : amplifiées)

40 00 UB (sorties non-bufférisées)

Série 74 :

74 C 00 (identique à la série 4000)

74 HC 00 (High-speed CMOS : CMOS rapides)

Caractéristiques de fonctionnement :

Gamme d’alimentation : de 3 V à 15 V.

Gamme de température : de – 40 °C à + 85 °C.

Puissance dissipée : environ 10 nW par porte.

Fréquence de fonctionnement : jusqu’à 12 MHz.

Sortance : jusqu’à 50 (série 4000B).

(Nombre d’entrées que l’on peut relier à une sortie de porte)

Excellente immunité aux bruits.

Caractéristique d ’Entrée/Sortie d’un inverseur

PORTES LOGIQUES CMOS

Fiche de référence

1

V

I

V

O

1

/

5

100%