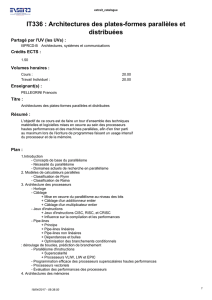

Architectures parallèles

Polytech Info 4 - Option parallélisme 1

Architectures parallèles

Daniel Etiemble

de@lri fr

de@lri

.

fr

Classification de Flynn

• Flot d’instructions x Flot de données

– Single Instruction Single Data (SISD)

– Single Instruction Multiple Data (SIMD)

– Multiple Instruction Single Data

– Multiple Instruction Multiple Data (MIMD)

• “Tout est MIMD” !

Polytech Info4 - Option parallélisme D. Etiemble 2

Polytech Info 4 - Option parallélisme 2

Architectures vectorielles

• Registres vectoriels

• Registres scalaires

• Chargement/rangement

vectoriel sans caches.

Permet les opérations de

scatter-gather

• Les instructions

vectorielles s’exécutent

élément par élément

dans les unités de calcul

Polytech Info4 - Option parallélisme D. Etiemble 3

Architectures vectorielles (2)

Polytech Info4 - Option parallélisme D. Etiemble 4

Code scalaire (64 itérations) Code vectoriel (registres

vectoriels de 64 éléments

Polytech Info 4 - Option parallélisme 3

Architectures vectorielles (3)

• Découpage des vecteurs

Si N > taille des registres vectoriels, on itère

• Instructions conditionnelles

–

Instructions vectorielles de comparaison

• Positionnent un vecteur de booléens

– Les instructions vectorielles n’exécutent

que les éléments pour lesquels le booléen

est vrai

– Les conditionnelles SI condition ALORS

…. SINON exécutent la suite des

instructions vectorielles avec le booléen

Vrai pour ALORS puis la suite des

instructions vectorielles avec le booléen

Faux pour SINON

• Chaînage des opérateurs.

Polytech Info4 - Option parallélisme D. Etiemble 5

Architectures vectorielles (4)

• Heures de gloires

– Machines vectorielles Cray…. (1975 : Cray-1)

• Disparition

–

Machines parallèles SIMD et MIMD

• Renaissance ?

– L’extension MIC du jeu d’instructions Intel

– 32 registres 512 bits (Zmm0 à Zmm31)

• 16 int32, 8 int64, 16 float, 8 double

– 8 registres de masque vectoriel k0 à k15 (16 bits)

• 1 bit par élément du registre Zmmi( 16 ou 8 bits)

–

Contrôle des opérations « élément par élément »

– Contrôle des écritures registre « élément par élément »

• Exception

– k0 correspond au « non masquage »

–DU SIMD au VECTORIEL

Polytech Info4 - Option parallélisme D. Etiemble 6

Polytech Info 4 - Option parallélisme 4

Architectures SIMD

• Modèle d’exécution

–CM2

– Maspar

Contrôleur

PE PE PEML ML ML

Lancement instructions

• Modèle obsolète pour machines parallèles

– Processeurs spécifiques différents des CPU standards

– Lancement des instructions incompatible avec les fréquences

d’horloge des microprocesseurs modernes

Shiti èh itti litti

Réseau d’interconnexion

Polytech Info4 - Option parallélisme D. Etiemble 7

–

S

ync

h

ron

i

sa

ti

on apr

è

s c

h

aque

i

ns

t

ruc

ti

on :

l

es

i

ns

t

ruc

ti

ons

conditionnelles sont synchronisées

• SPMD

•Extensions SIMD dans les microprocesseurs

Version SPMD du SIMD

• Modèle d’exécution

CPU CPU CPUML ML ML

– Chaque CPU exécute le même code.

– Les CPU sont synchronisés par des barrières avant les transferts

de données.

Réseau d’interconnexion

If condition

Polytech Info4 - Option parallélisme D. Etiemble 8

L11 LI2

If

condition

Liste instructions 1

ElseListe instructions 2

Suite

Polytech Info 4 - Option parallélisme 5

Les architectures MIMD

Mémoire Multiprocesseurs

-O

p

enMP…

PE PE

Réseau

PE

p

- Pthreads…

Réseau

Polytech Info4 - Option parallélisme D. Etiemble 9

PE PE PE

Mémoire

Mémoire

Mémoire

Multi-ordinateurs

- MPI (passage de

messages)

Multi-thread et Multiprocesseur

Polytech Info4 - Option parallélisme D. Etiemble 10

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

1

/

25

100%