Sujet de thèse – Contrat Doctoral Unique Contexte

Sujet de thèse – Contrat Doctoral Unique

Nouvelles fonctions de gate driver CMOS pour transistors de puissance grands gaps : contrôle

rapproché, surveillance et protection ultra-rapide, récupération d’énergie

Mots clés : conception CMOS, électronique analogique, électronique de puissance, commande de transistors

grands gaps, MOSFET SiC et HEMT GaN, onduleur de tension, synchronous buck-boost

Contexte :

Les transistors de puissance grands gaps tels que les MOSFETs en Carbure de Silicium (SiC) et les

transistors à haute mobilité électronique (HEMT) en Nitrure de Gallium (GaN) repoussent les

compromis classiques en électronique de puissance. Particulièrement dans les applications

embarquées et le marché « grand public » de l’électronique de puissance (composants 600V-1200V),

des gains significatifs ont été démontrés par les transistors SiC et GaN : meilleurs rendements, couplés

à une augmentation des densités de puissance offerte par la montée en fréquence de découpage.

La mise en œuvre de semi-conducteurs grand-gap fait aussi émerger des besoins spécifiques de

surveillance et de protection ultra-rapides, en particulier pour les convertisseurs de forte puissance et

dans les applications critiques en termes de sûreté de fonctionnement. Les solutions appliquées

aujourd'hui sur les semi-conducteurs rapides en silicium font appel à une électronique haute tension

peu intégrable dans un "gate driver" et caractérisée par un compromis "rapidité – robustesse"

incompatible à nos yeux avec les spécificités des semi-conducteurs grand-gap. Il nous semble donc

pertinent d'aborder cette problématique en partant d'une électronique basse tension et en exploitant

directement et uniquement les tensions et courants de grille des semi-conducteurs grand-gap

considérés, aussi bien sur les séquences de commutation que durant les régimes établis :

par le traitement du courant de grille (en amplitude crête, en valeur intégrale ou "gate-charge" [1],

en valeur sur régime établi) et nous permettre de détecter une température de jonction

anormalement élevée, un défaut de comportement durant les séquences de commutation (court-

circuit) voire même un niveau avancé de vieillissement de l'oxyde de grille,

la prise en compte de la tension de grille, seule ou couplée à celle du courant de grille, doit nous

permettre de rendre plus robuste les détections, i.e. obtenir une moindre dépendance au point de

fonctionnent du convertisseur et aussi, par échantillonnage sur des séquences particulières, de

reconstruire la variation du courant de charge.

Cette approche est gage d'intégrabilité au sein même de l'ASIC CMOS "gate-driver" et doit nous

permettre d'accéder à des niveaux de performance, de coût et de reproductibilité inégalés par rapport

à des solutions à composants discrets, de surcroit si ceux-ci sont en technologie haute tension. Dans

ce contexte, ce travail de recherche se focalise particulièrement sur la conception d’un circuit ASIC

CMOS de commande rapprochée permettant d’intégrer de nouvelles fonctions pour aller au-delà des

performances disponibles sur le marché (immunité aux transitoires de mode commun – CMTI [2] au-

delà de 200V/ns, gestion et optimisation de la consommation énergétique, récupération et transfert

d’énergie, surveillance et protections ultra-rapides).

Actions de recherche :

Le travail de thèse s’appuiera sur une étude bibliographique et une veille scientifique et technique

continue, afin de dégager et confirmer les limites des solutions et approches existantes. Le-La

doctorant-e effectuera la conception, le dimensionnement et le routage de circuits analogiques et

numériques sur une technologie CMOS industrielle déjà identifiée. La ou les puces CMOS conçues

proposeront des fonctions intégrées telles que : techniques de récupération d’énergie électrique,

transfert d’énergie et communication par voie optique, observation robuste et protection ultra-

rapide via une intégration fonctionnelle, techniques d’optimisation de la consommation d’énergie et

d’adaptation. Au-delà d’un travail de conception microélectronique CMOS, le-la doctorant-e devra

prendre en compte les spécificités et les aspects multi-physiques de l’électronique de puissance et des

interactions entre « gate driver » et cellule de commutation de puissance, en particulier sur des circuits

tests de type onduleur deux niveaux et multiniveaux intégrés (ayant des fréquences de commutation

de l'ordre de la centaine de kHz à quelques MHz).

Ces actions de recherche, en lien avec une dynamique internationale forte et de grandes attentes du

monde industriel, devront s’appuyer sur des caractérisations expérimentales poussées et rigoureuses :

depuis la caractérisation de fonctions CMOS sous pointes jusqu’à l’implémentation dans des cellules

de commutation "test" représentatives des convertisseurs fortement intégrés, en basse et moyenne

tension, étudiés ou en perspective dans le groupe CS du LAPLACE. Le spectre couvert dans ce travail

de recherche est donc particulièrement large. En ce sens, des candidat-e-s pluri-disciplinaires et à forte

capacité d’adaptation sont recherché-e-s.

Compétences recherchées :

Une grande partie du travail de recherche étant focalisé sur la conception de fonctions intégrées en

technologie CMOS, les candidat-e-s devront justifier de compétences dans la conception, simulation,

dimensionnement et routage analogique et numérique en technologie CMOS. Des connaissances sur

l’électronique de puissance, la physique du semiconducteur et la commande des transistors de

puissance seront très appréciées.

Le-La doctorant-e devra démontrer un goût pour la recherche, l’esprit d’initiative et une rigueur

expérimentale. Pendant son séjour de 36 mois au laboratoire, le-la doctorant-e pourra acquérir de

nombreuses compétences en bénéficiant de l’environnement dynamique et du savoir-faire reconnu

de l’encadrement et du groupe de recherche.

Laboratoire et encadrement :

Laboratoire plasma et conversion d'énergie LAPLACE

Site ENSEEIHT - 2, rue Charles Camichel - BP 7122 - 31071 Toulouse cedex 7- France

Groupe Convertisseurs Statiques - http://www.laplace.univ-tlse.fr/research-

groups/convertisseurs-statiques/

Directeur de thèse :

Dr. Nicolas ROUGER, Chargé de recherche CNRS, Habilité à Diriger des Recherches

Tél. +33 5 34 32 24 00, [email protected]

Co-directeur de thèse :

Dr. Frédéric RICHARDEAU, Directeur de recherche CNRS, Habilité à Diriger des

Recherches

Tél. +33 5 34 32 23 98, frederic.richardeau@laplace.univ-tlse.fr

Références :

[1] T. Horiguchi, S. i. Kinouchi, Y. Nakayama and H. Akagi, "A fast short-

circuit protection method using gate charge characteristics of SiC

MOSFETs," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, 2015, pp. 4759-4764.

[2] N. Rouger, L. T. Le, D. Colin and J. C. Crébier, "CMOS SOI gate driver with integrated optical supply and optical

driving for fast power transistors," 2016 28th International Symposium on Power Semiconductor Devices and ICs

(ISPSD), Prague, 2016, pp. 427-430.

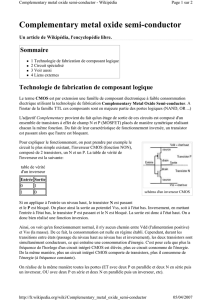

Exemple de travaux précédents au laboratoire LAPLACE

(zoom sur une fonction analogique intégrée en

technologie CMOS 180nm pour les gate driver)

1

/

2

100%