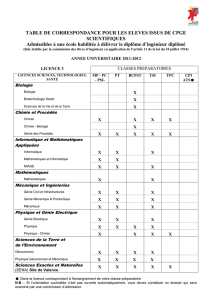

Architecture des systèmes à processeurs – IUT GEII (ISI-II2) -2

19/03/2009

1

Architecturedessystèmes à

processeurs – IUTGEII(ISI‐II2)‐2

ChristopheBLANC

www.christophe‐blanc.info

IUTdeMontluçon

Département Génie Electrique etInformatique

Industrielle

È

’

Architecturedessystèmes àprocesseurs

MOD

È

LE DEPROGRAMMATION D

’

UN

PROCESSEUR

I.U.T.Montluçon—DépartementGénieElectriqueetInformatiqueIndustrielle—2

19/03/2009

2

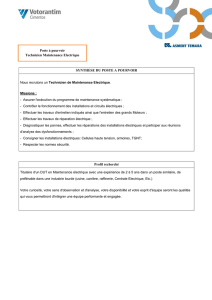

Codaged’uneinstructionM32C87Renesas

MOV.size:GSource,Destination

1101000110010011

C98B

MOV.W:GR2,R0;TransférercontenudeR2dansR0

Exécutiond’unprogramme

élémentaire(notationsymbolique)

AdresseProgrammeSourceAssembleur

Étiquette Opération Opérande Commentaire

ADD.W R1,R0 ;R0<‐R0+R1

$FE0304 AdDeb

MOV.W R0,R1 ;R1<‐R0

$FE0306

MOV.W R0,‐2[SP] ;‐2(SP)<‐D0

$FE0307

JMP AdDeb ;PC<‐AdDeb

$FE030A

Mnémoniquesàlaplace

ddébi i

Zone mémoire réservée

I.U.T.Montluçon—DépartementGénieElectriqueetInformatiqueIndustrielle—4

d

e

d

onn

é

es

bi

na

i

res

Zone

mémoire

réservée

auxinstructions

19/03/2009

3

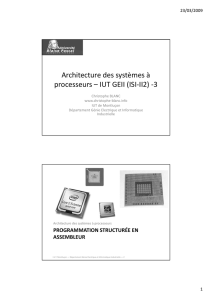

PC

Exécutionduprogramme

Instruction:ADD.W R1, R0

Mémoireréservée

auxinstructions

F

E

0304

R0

R1

RI

Rechercher

Instruction MOV.W R0,R1

MOV.W R0,‐2[SP]

JMP.B AdDeb

$FE0304

$FE0306

$FE0307

$FE030A

FE0304

0013

0022

ADD.W R1,R0

I.U.T.Montluçon—DépartementGénieElectriqueetInformatiqueIndustrielle—5

PC

D0

D1RI

Exécuter

Instruction

$000700

$000702

Mémoireréservée

auxdonnées

ADD.WR1,R0

FE0304

0013

0022

ADD

+2

FE0306

0035

PC

Exécutionduprogramme

Instruction:MOV.W R0, R1

Mémoireréservée

auxinstructions

F

E

0306

R0

R1

RI

Rechercher

Instruction

ADD.W R1,R0

MOV.W R0,‐2[SP]

JMP.B AdDeb

$FE0304

$FE0306

$FE0307

$FE030A

F 0306

0035

0022

MOV.W R0,R1

I.U.T.Montluçon—DépartementGénieElectriqueetInformatiqueIndustrielle—6

PC

D0

D1RI

Exécuter

Instruction

$000700

$000702

Mémoireréservée

auxdonnées

MOV.WR0,R1

FE0306

0035

0022

+1

FE0307

0035

19/03/2009

4

PC

Exécutionduprogramme

Instruction:MOV.W R0, -2[SP]

Mémoireréservée

auxinstructions

F

E

0307

R0

R1

RI

Rechercher

Instruction

ADD.W R1,R0

MOV.W R0,R1

JMP.B AdDeb

$FE0304

$FE0306

$FE0307

$FE030A

FE0307

0035

0035

MOV.W R0,‐2[SP]

I.U.T.Montluçon—DépartementGénieElectriqueetInformatiqueIndustrielle—7

PC

R0

R1

RI

Exécuter

Instruction

$000700

$000702

Mémoireréservée

auxdonnées

MOV.WR0,‐2[SP]

FE0307

35

35

+3

FE030A

3500

SP‐>

PC

Exécutionduprogramme

Instruction:JMP.B AdDeb

Mémoireréservée

auxinstructions

F

E

030A

R0

R1

RI

Rechercher

Instruction

ADD.W R1,R0

MOV.W R0,R1

MOV.W R0,‐2[SP]

$FE0304

$FE0306

$FE0307

$FE030A

F 030A

0035

0035 JMP.B AdDeb

I.U.T.Montluçon—DépartementGénieElectriqueetInformatiqueIndustrielle—8

PC

R0

R1

RI

Exécuter

Instruction

$000700

$000702

Mémoireréservée

auxdonnées

JMP.BAdDeb

FE030A

0035

0035

+2

FE030C

3500

FE0304

19/03/2009

5

TypesdeDonnées

•LeµPtraitedesdonnéesbinairesnontypées

–

C’estle

p

ro

g

rammeur

q

uidéfinitlet

yp

edesdonnées

pg qyp

manipuléespar:

•lechoix desinstructions,

•lalogique del ’algorithme.

•Lesinstructionstraitentlesdonnéessuivantes:

–Entierssignés sur8,16,ou32bits

I.U.T.Montluçon—DépartementGénieElectriqueetInformatiqueIndustrielle—9

–Entiersnonsignés sur8,16,ou32bits

–String

–Nombresexprimésenvirguleflottante(réels)

DataArrangement

DataArrangementinRegister

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

1

/

18

100%