1. Utiliser un Système à Microprocesseur

Royaume du Maroc

OFFICE DE LA FORMATION PROFESSIONNELLE ET DE LA PROMOTION DU TRAVAIL

Première Année

Programme de Formation des Techniciens Spécialisés en

Électronique

DIRECTION DE LA RECHERCHE ET INGENIERIE DE LA FORMATION

Septembre 1995

MODULE 11

Introduction aux Microprocesseurs

Résumé de Théorie

Télécharger tous les modules de toutes les filières de l'OFPPT sur le site dédié à la formation professionnelle au Maroc :

www.marocetude.com

Pour cela visiter notre site www.marocetude.com et choisissez la rubrique : MODULES ISTA

INTRODUCTION AUX MICROPROCESSEURS

RÉSUMÉ DE THÉORIE

Utiliser un Système à Microprocesseur.

TECCART INTERNATIONAL 2000 inc.

3155, boul. Hochelaga,

Montréal, Québec (Canada)

H1W 1G4

RÉDACTION

Serge Leblanc.

DESSINS ET CONCEPTION GRAPHIQUE

Serge Leblanc

RÉVISION TECHNIQUE

Pierre Asselin B.Sc. & Christian Lépine

RÉVISION LINGUISTIQUE

François Gaudreau

COMMISSION DE VALIDATION

Formateurs de l'OFPPT

Les droits de reproduction et de diffusion de ce document sont cédés par Teccart

International 2000 inc. à l’Office de la Formation Professionnelle et de la Promotion

du Travail du Royaume du Maroc, pour sa propre utilisation au Maroc.

Mis à part l’OFPPT, toute reproduction, en tout ou en partie, par quelque procédé

que ce soit, est interdite.

Mp_Rt1.Doc, imprimé à Montréal, le 26 mai 2017

TABLE DES MATIÈRES

1. UTILISER UN SYSTEME A MICROPROCESSEUR 1-1

1.1 Architecture interne d’un système à microprocesseur 1-1

1.1.1 Le microprocesseur 1-1

1.1.2 La mémoire 1-1

1.2 Les entrées/sorties 1-2

1.3 Les bus de communication 1-2

1.3.1 Le bus de données 1-2

1.3.2 Le bus d’adresses 1-2

1.3.3 Le bus de contrôle 1-2

1.4 Le microprocesseur 6809 1-3

1.4.1 Brochage du MC6809 1-3

1.4.2 Alimentation 1-4

1.4.3 Xtal et Extal 1-4

1.4.4 E et Q 1-4

1.4.5 RESET 1-4

1.4.6 MRDY 1-5

1.4.7 Bus de donnée D0 à D7 1-5

1.4.8 Bus d’adresses A0 à A15 1-5

1.4.9 R/W 1-5

1.4.10 /HALT 1-5

1.4.11 DMA/BREQ 1-6

1.4.12 BA et BS 1-6

1.4.13 NMI, FIRQ, IRQ 1-7

1.5 Décodage des adresses 1-7

1.5.1 Analyse d’un décodeur d’adresses 1-7

1.5.2 Cartographie du système Mod. E6809 1-8

1.5.3 Présentation de la cartographie 1-9

1.6 Architecture interne du microprocesseur 6809 1-10

1.6.1 L'unité arithmétique et logique 1-11

1.6.2 Les registres du 6809 1-11

1.7 Exercices 1-13

Résumé de Théorie Introduction aux Microprocesseurs

Système à Microprocesseur page 1-1 OFPPT/TECCART

1. Utiliser un Système à Microprocesseur

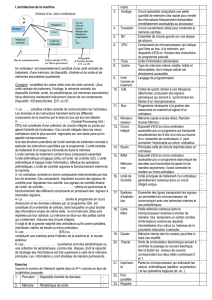

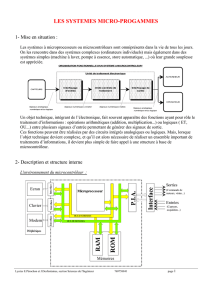

1.1 Architecture interne d’un système à microprocesseur

L'architecture interne d'un ordinateur se compose essentiellement de trois blocs: le

microprocesseur, la mémoire et les entrées/sorties reliées entre elles par trois bus de

communication; le bus de données, le bus d’adresses et le bus de commande.

Bus de données (8 lignes)

Mémoire

Unité centrale de

traitement

microprocesseur

Entrées/Sorties

Bus de contrôle

Bus d'adresses

Figure 1-1 Architecture interne d’un ordinateur

1.1.1 Le microprocesseur

Un microprocesseur est l'implantation en un seul boîtier, en technologie LSI ou VLSI,

d'une unité centrale de traitement de données CPU et d’une unité arithmétique et logique

ALU. Son principal travail est de fournir aux autres éléments, qui lui sont raccordés, la

synchronisation nécessaire et fonctionnelle du traitement des informations qui lui sont

acheminées.

1.1.2 La mémoire

C'est la partie où l'on retrouve les programmes exécutables et les données à traiter. Cette

section est subdivisée en deux; d'une part, il y a la mémoire latente et d'autre part, la

mémoire vive.

Mémoire morte

C'est la mémoire de lecture; elle contient le programme du système. L'avantage de la

ROM (Read Only Memory), c’est d'être permanente; son contenu ne disparaît pas quand

le système n'est plus alimenté. La ROM contient toujours un programme de chargement

initial ou un moniteur pour permettre le fonctionnement du système dès la mise sous

tension. Dans un contexte de contrôle de processus, presque tous les programmes

résideront en ROM car ils seront rarement changés et devront être protégés des pannes

d'alimentation.

Résumé de Théorie Introduction aux Microprocesseurs

Système à Microprocesseur page 1-2 OFPPT/TECCART

Mémoire vive

C'est la mémoire de lecture et d’écriture du système ou RAM (Random Access Memory).

Le contenu de ce type de mémoire est perdu lorsque l'on coupe l'alimentation. La

mémoire vive (RAM) doit être chargée, avant utilisation, à partir du clavier ou à partir

d’une mémoire de masse comme, par exemple, une unité à ruban magnétique ou une

unité à disque.

1.2 Les entrées/sorties

Les entrées/sorties sont nécessaires pour que le microprocesseur communique avec le

monde extérieur et, évidemment, avec l'utilisateur. Il serait tout à fait inutile de réaliser un

ordinateur sans qu'il y ait quelques entrées et quelques sorties afin de communiquer avec

l'extérieur.

1.3 Les bus de communication

Évidemment, pour que le système fonctionne, il doit y avoir une communication entre le

microprocesseur, la mémoire et les entrées/sorties. Cette communication est réalisée à

l'aide de trois bus qui regroupent les signaux, selon leur fonction.

1.3.1 Le bus de données

C'est un bus bidirectionnel (de 8 bits pour un 6809) sur lequel transitent les données

échangées par les éléments du système.

1.3.2 Le bus d’adresses

Il s'agit d'un bus unidirectionnel (de 16 bits pour un 6809), émanant du microprocesseur

et se propageant vers les dispositifs qu'il peut adresser. L'adresse qu'il porte permet

d'atteindre une case mémoire ou un registre spécifique avec laquelle une opération est

désirée.

1.3.3 Le bus de contrôle

C'est un groupe de lignes issues de ou allant vers le microprocesseur et reliant ce dernier à

d'autres dispositifs. Son rôle est de véhiculer les signaux destinés à assurer la

synchronisation et la commande de l'ensemble du système. Par exemple, la ligne Reset et

R/W (lecture/écriture), les lignes d'interruptions et l'horloge appartiennent à ce bus.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%