COURS D`ARCHITECTURE DES ORDINATEURS

COURS D’ARCHITECTURE DES ORDINATEURS

Chapitre 6 : Les Entrées-Sorties

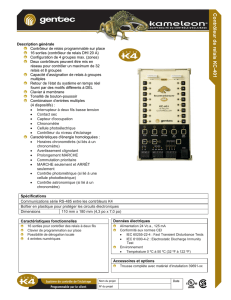

Contrôleurs d’E/S :

-Rôles :

Il sert à la communication entre le monde extérieur et le “monde CPU”. C’est un petit

automate (processeur) qui a la charge d’un périphérique.

Il doit régler les problèmes dus à l’asynchronisme de vitesse, il utilise alors de la

mémoire tampon. Il doit avoir des possibilités de stockage de données donc de la mémoire :

stockage dans des registres.

Il doit transcoder les données fournies par le monde extérieur (la couche physique est

traité par un contrôleur d’E/S).

-Caractéristiques :

On peut avoir des contrôleurs : simple, au minimum 1 bistable

: complexe, sophistiqué, plus complexe qu’un CPU (Ex :

contrôleur Ethernet)

Un CPU travaille toujours, il a un fonctionnement d’enchaînement d’instructions,

tandis qu’un contrôleur d’E/S fait son instruction et s’arrête (en prévenant qu’il a fini).

-Structure :

Architecture générale :

Le contrôleur d’E/S n’a pas de PC (Compteur de Programme), il faut lui donner

l’adresse où chercher les instructions.

Modèle de programmation :

-registres de commandes : configurer le travail à faire.

-registres de données : mémoires tampons pour l’échange des données.

-registres accessibles par les instructions de lecture-écriture dans l’espace des E/S.

Les PORTS sont des fils, il y a conversion binaire-signal et signal-binaire.

Exemple d’handshake : vérifier si le périphériques et prêt.

-Espace mémoire d’E/S :

Il faut avoir 2 espaces mémoire différents : un espace de mémoire centrale (RAM) et

un espace mémoire d’E/S.

L’idéal serait d’avoir deux chemin différents, soit un BUS de plus, mais on utilise

jamais les 2 mémoires en même temps donc un seul BUS suffit. Mais il faut quand même

différencier les 2 mémoires, on utilise donc un bit de plus sur le CPU.

Il y a deux structures différentes :

-Intel :

2 types d’instructions move différentes ( 1 pour la RAM et 1 pour les E/S.)

instructions spécifiques :

I/O Input/Output Mem*/IO vrai

RAM move Mem*/IO faux

-Motorola :

Il utilise une autre méthode : il place le contrôleur d’E/S dans la RAM. Celui-ci ne doit

pas répondre aux instructions comprises entre … et … . On diminue alors la mémoire, la

RAM ( de quelques Ko).

1seule instruction move RAM-I/O

réserver une plage pour les I/O

La deuxième méthode fait diminuer la mémoire mais on utilise quand même car la

taille maximale de la mémoire d’E/S n’a pas varié depuis 50 ans ( de l’ordre de 64Ko). Avant,

il y avait 64Ko de RAM ( pour un processeur 8 bits) mais maintenant on a 4Go de RAM

(processeur 32 bits).

-E/S : mémoire distribué, éparse.

-Adressage des E/S :

Adressage du type “géographique”, mémoire éparse ( non-contigüe), hiérarchisée.

On ne considère plus les 16 bits d’adresse à des adresses consécutives, on les

regroupent par champs associés à des “zones géographiques”.

POIDS FORTS poids faibles

Ex : adresse carte Ex : adresse registre

Ex : n° de ville Ex : n° de rue

-Ports d’E/S :

Si on veut communiquer avec le contrôleur d’E/S, il faut connaître son adresse (elles

se trouve dans la notice). Sur chacune des cartes, il y a un système de décodage pour

distribuer au contrôleur d’E/S.

Inconvénients : pour changer les adresses, on doit ouvrir la machine et échanger les

cavaliers. Maintenant on cherche à le faire depuis l’intérieur en utilisant un programme, on

utilise plus de cavaliers mais de la mémoire non-volatile. C’est le système Plug-and-Play. Il y

a donc des pages d’adresses réservées.

-Techniques d’E/S :

Il faut prendre en compte l’environnement externe : lecture-écriture. Si on veut écrire

deux instructions à la suite, on aura une perte de la deuxième à cause des différences des

temps d’exécution et de lecture ; la deuxième instruction sera lu alors que la première n’aura

pas fini d’être exécuter. Il faut donc synchroniser soit en attendant (le polling) , soit avec un

mécanisme de signalisation par interruptions. Le polling est plus rapide mais moins efficace.

Pour le transfert de données, on utilise ce mode :

mem CPU registre d’E/S

Ces deux méthodes sont utilisées pour les transfert de données à faible débit.

Mais pour les pour les transfert de données à haut débit on utilise un contrôleur d’E/S

spécial : un DMA (Accès Direct à la Mémoire). On utilise alors ce mode :

mem registre d’E/S

Si on utilise un DMA, il faut empêcher le CPU de travailler, on le fait à l’aide d’un fils

branché directement sur le CPU, le DMA lui “pique” l’horloge et lui rend quand il a fini.

-Polling :

Caractérisé par la période de scrutation (il faut regarder périodiquement si le

contrôleur d’E/S a fini). C’est un inconvénient car il faudrait mélangé un programme dans un

autre. Autre caractéristique : combien de temps regarder ? Pour être le plus efficace possible,

il faudrait scruter constamment, on appelle cela de l’attente active. On introduit un temps de

latence (temps entre deux périodes).

-Interruptions :

Séparer les 2 programmes : un pour le travail habituel et un autre dédier au problème

Ce mécanisme a aussi un temps de latence car il faut sauvegarder des registres. Dans

ce cas, le temps de latence est plus grand que dans le cas d’attente active.

Quand un contrôleur d’E/S renvoie une interruption c’est pour signaler qu’il a fini son

travail et qu’il peut en faire une autre.

On peut partager un même niveau d’IT (même vecteur d’IT) pour différents

périphériques.

Pour voir quel périphérique est la cause de l’interruption, il faut aller voir sur tous les

périphériques partageant l’IT, on exécute alors une scrutation. C’est intéressant lorsque l’on a

à faire à des périphériques identiques.

-DMA :

Les échanges d’E/S : RAM reg_E/S utilisent les instructions d’E/S . Tout passe

par le CPU. Si la quantité de données est importante : on a un CPU mal adapté qui effectue

beaucoup de cycles mémoires. Pour résoudre ce problème, on utilise un DMA (Direct

Memory Access) qui est spécialisée dans le transfert : mem mem et mem reg_E/S.

Caractéristiques : -efficace mais concurrent du CPU sur le BUS ( produit des

adresses), fonctionnement bloquant, vol de cycle, interruptions.

-DMA définit par un canal (de transfert), en général 2 par contrôleur

DMA. -Déconseillé pour un système multitâches.

CCL : Pour ajouter des périphériques, il faut donner l’adresse, du contrôleur d’E/S, au

pilote (driver) du périphérique en question. L’adresse doit être unique. Puis on doit configurer

l’adresse sur la carte (cavaliers ou logiciels) et paramétrer le pilote, ceci est généralement fait

par les programmes d’installations. Vrai pour les contrôleurs de mémoire vidéo.

Il ne faut pas que le contrôleur vidéo et le CPU ne travaille en même temps, il y a

priorité. On utilise, pour le contrôleur vidéo, la mémoire présente sur la carte vidéo. S’il y a

une mémoire partagée, il faut le dire au CPU et donc exclure toute écriture, il faut également

indiquer au pilote vidéo l’adresse de cette mémoire.

Pour afficher une image, il faut plus de mémoire que celle présente sur la carte vidéo

(64Ko) (1024×768×32bits). Il faut faire petits bouts par petits bouts. La mémoire partagée est

la même sur la carte vidéo.

-Exemples d’E/S :

-Interface parallèle

-Liaison Série UART, UART 8251

-Temporisateur-Timer

-Circuit Horloge Temps Réel :

Permet de lire l’heure, ce lit comme une mémoire d’E/S et est la seul manière

d’obtenir une mesure de temps précise car ce circuit es autonome du S.E.

1

/

5

100%