Vie des exécutables - Site pédagogique / Systèmes électroniques

Structure des systèmes

programmables

Bonjour systèmes embarqués

Alexis Polti

1 décembre 2015 © 2015 Alexis Polti SE203

page 2

Licence de droits d'usage

Par le téléchargement ou la consultation de ce document, l’utilisateur accepte la licence d’utilisation qui y est

attachée, telle que détaillée dans les dispositions suivantes, et s’engage à la respecter intégralement.

La licence confère à l'utilisateur un droit d'usage sur le document consulté ou téléchargé, totalement ou en partie, dans

les conditions définies ci-après, et à l’exclusion de toute utilisation commerciale.

Le droit d’usage défini par la licence autorise un usage dans un cadre académique, par un utilisateur donnant des cours

dans un établissement d’enseignement secondaire ou supérieur et à l’exclusion expresse des formations commerciales

et notamment de formation continue. Ce droit comprend :

●le droit de reproduire tout ou partie du document sur support informatique ou papier,

●le droit de diffuser tout ou partie du document à destination des élèves ou étudiants.

Aucune modification du document dans son contenu, sa forme ou sa présentation n’est autorisé.

Les mentions relatives à la source du document et/ou à son auteur doivent être conservées dans leur intégralité.

Le droit d’usage défini par la licence est personnel, non exclusif et non transmissible.

Tout autre usage que ceux prévus par la licence est soumis à autorisation préalable et expresse de l’auteur :

alexis.polti@telecom-paristech.fr

Contexte académique } sans modification

1 décembre 2015 © 2015 Alexis Polti SE203

page 3

tl;dr

Ce qu'on va apprendre :

le vocabulaire et les structures de base

des systèmes embarqués,

que tout est soit processeur soit mémoire,

que code et variables ont généralement

deux adresses : LMA et VMA,

ce qui se passe avant et après main(),

ce que fait un bootloader,

les différentes façons de débugger.

1 décembre 2015 © 2015 Alexis Polti SE203

page 4

Plan

Les systèmes à processeur

architecture, mapping mémoire

modes d'exécution et exceptions

types de systèmes : bare metal vs. hosted

vie des exécutables

bootloaders

debug

1 décembre 2015 © 2015 Alexis Polti SE203

page 5

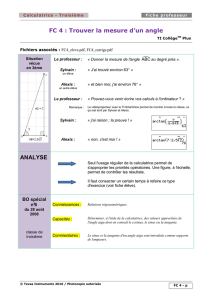

Architecture globale

processeur

entrées

sorties

interface mémoire

mémoire réelle

µContrôleur

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

1

/

75

100%