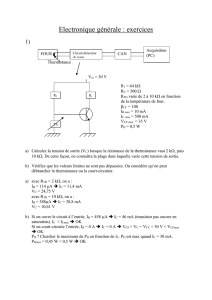

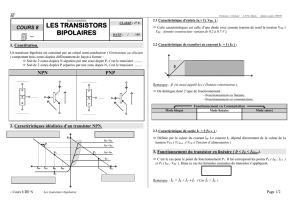

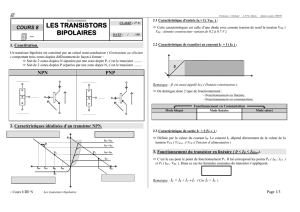

Transistors bipolaires en commutation

Transistors bipolaires en commutation

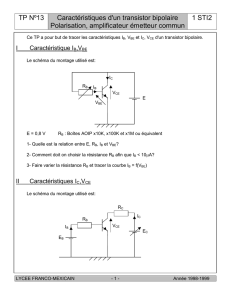

NPN

Avec la tension d’alimentation E et la charge R, la relation courant-tension d’un transistor

bipolaire devient :

CE

C

E V

I

R

−

=

D’où la droite de charge. Le point B, intersection de cette droite avec la caractéristique I

B

= 0,

correspond au blocage, le point S à la saturation, obtenue de façon certaine si :

+

VCE

VBE

IC

+ E

IB

R

B

E/R

IC

ICM

IC

0 VCE

1

100

µ

s

1ms

10

µ

s

2

3

4

S

log VCE VCE0

log IC

ICM

IC

0

1

2

3

4

10

µ

s

100

µ

s

1ms

sat

0min 0min

ou

β β

c

B B

I

E

I I

R

≥ ≥

Quel que soit le point de fonctionnement déterminé par I

B

, E et R, il faut veiller qu’il soit à

l’intérieur de l’aire de sécurité représentée en trait fort (SOA ou safe Operating Area). Si le

courant de base est I

b

variable et que le point de fonctionnement se déplace périodiquement sur

la droite de charge ou sur une courbe différente (Z

≠

R), l’aire de sécurité est agrandie au

contour en tirets (FBSOA ou Forward Biased Safe Operating Area) dont certaines limites ne

peuvent être atteintes que pendant les durées spécifiées (en général 1 % de la période pour T

b

=

25°C et T

j

= T

iM

, parfois 50 % de la période pour T

b

= 70°C et T

j

= T

iM

, de toute façon T

j

ne doit

pas dépasser T

jM

même un court instant et doit rejoindre sa valeur normale avant une nouvelle

impulsion. L’aire de sécurité est limitée soit par I

C

, soit par I

CM

(1), la puissance maximale (2),

le "second claquage" c’est-à-dire la risque de répartition hétérogène du courant (3), V

CE0

(4)

.

Quand le transistor est bloqué (I

B

= 0) la tension V

CE

peut atteindre V

CES

si I

B

<

0 (NPN) elle

peut aller jusqu’à V

CEX

et l’aire de sécurité est accrue (RBSOA ou Reverse Biased Safe

Operating Area) mais la surface supplémentaire doit être traversée rapidement. Pour des

surcharges accidentelles le courant peut atteindre I

CP

(FBAOA et RBAOA ou Forward et

Reverse Biased Accidental Overlord Area).

Au blocage la puissance dissipée est :

CE0 0 CB0 CB0

β si 0, si 0 (NPN).

B B B B

P EI E I I P EI I

= = = = ≤

A la saturation :

sat sat

S CE c

P V I

=

+

VCE

IC

+ E

Ib

R

A

Ib

IB1

t

IB2

t

IC

0

tm

90%

IC

td

10

%

Si les commutations ont lieu avec une charge résistive (dessin A ci-dessus) la somme des

puissances dissipées pendant ces commutations est :

2

on off

0, 21 ( ) .

m d

E

P P t t f

R

+ = +

Avec une charge inductive et la diode de

"roue libre" D, nécessaire pour que le blocage du

transistor ne provoque pas une énorme surtension à ses bornes car le courant I au lieu d’être

brusquement interrompu circule dans la diode. Les variations de V

ce

et I

c

sont compliquées et

ne sont guère accessibles à un calcul analytique. En les approximant (dessin B), les puissances

dissipées sont :

on off

, .

CEM M m d

P V I t f P EIt f

= =

IC, VCE

VCEM

IM

I

0

0,9I

IC

VCE 0,1I

td

tm

t

+

v

C

A

RB1 RB2

r

+

VCE

L

IC

+ E

IB

ID

B

Afin de diminuer les puissances P

on

et P

off

, il y a moyen de diminuer t

m

et t

d

. Avec le schéma A

ci-dessus, I

b

passe par une pointe pratiquement égale à

1

B

V

R

avant de redescendre à

1 2

B B

V

R R

+

avec une constante de temps voisine de

1 2

1 2

B B

B B

R R C

R R

+

, ceci réduit suffisamment

t

m

pour que malgré

l’augmentation de

I

M

,

P

on

soit diminuée. Le temps

t

d

est réduit si le transistor n’est pas en

sursaturation mais à la limite de la saturation. Ceci est assuré par l’un ou l’autre des schémas

B; quand le courant

I

b

croît,

T

approche de la saturation,

V

CE

décroît et tend vers

V

CEsat

, la

différence de potentiel

v – V

CE

est alors telle que

D’

conduise, le courant

I

B

cesse de croître et

V

CE

s’établit à :

(

)

(

)

2 B1 ; B2 ;

CE BE D D CE BE D D

V V V V V V V V

′ ′

= + − = + −

La diode

D’’

assure le passage inverse au blocage.

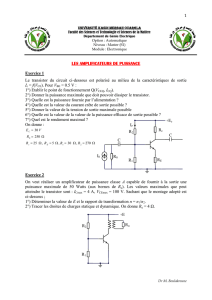

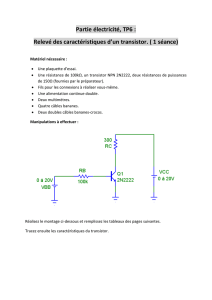

Exercices

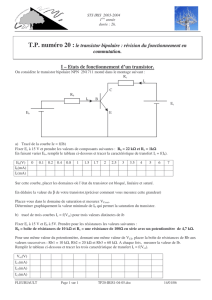

Ex.1 Un transistor pour lequel

0max

20

β

=

et

0

2

CE

I mA

= est commuté de l’état bloqué à l’état

saturé conformément aux courbes ci-dessous.

E

= 200 V,

R

C

= 20 Ohms.

a) Calculer le courant base à fournir pour obtenir la saturation.

b) Calculer les puissances dissipées pendant la saturation et le blocage pour

1 1 3

, ,

4 2 4

α

=

1V,

CE sat C sat

C

E

V I

R

= =

en négligeant

t

m

et

t

d

.

c)

Calculer la puissance dissipée pendant les commutations aux fréquences de 10 kHz et

100 kHz si

t

m

= t

d

= 0,2 µs

(négliger la puissance dissipée dans le circuit de base),

comparer avec les puissances précédentes.

2

×

D

D’

B1

v

D’’

D

D’

B2

v

D’’

Réponse

a)

0min

C

B

I

I

β

= et, à la saturation

0,5 A.

C B

C

E

I I

R

=

⇒

=

(trier les transistors pour ne pas sursaturer ceux qui ont un plus grand

0

β

ou utiliser un

circuit anti-sursaturation).

b)

2,5 W; 5 W; 7,5 W.

sat CE sat C sat

P V I

α

= =

(

)

( )

0

0

0

1 0,3 W; 0,2 W; 0,1 W si 0.

1 15 mW; 10 mW; 5 mW; si 0

b CE B

CE

B

P EI I

EI I

α

αβ

= − = =

= − = <

c) En ne tenant pas compte des variations de

α

T

dues à

I

m

et

I

d

, les puissances

précédentes ne changent pas, mais s’y ajoute

P

on

+ P

off

dont la valeur croît avec la

fréquence.

Puissances dissipées pendant les commutations :

2

on off

0, 21 ( ) .

m d

E

P P t t f

R

+ = +

à 10 kHz : 1,68 W

à 100 kHz : 16,8 W

La puissance dissipée pendant les commutations atteint 17 W à 100 kHz alors que la

puissance dissipée en dehors des commutations est au plus de 7,5 W.

t

ICsat

0

t

m

90%

IC

t

d

10

%

IB

t

0

v

t

T

0

α

T

v

E

IC

RC

RB

I

B

+

-

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

1

/

14

100%