information to users - Bibliothèque et Archives Canada

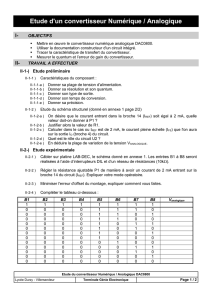

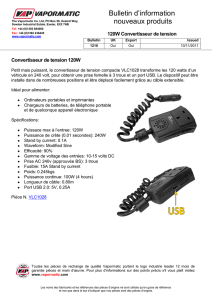

publicité