Le niveau ISA

Le niveau ISA ou la

macroarchitecture

•Les programmes ISA sont interprétés sur la

microarchitecture par le microprogramme.

•Pile

•Modèle mémoire

•Jeux d'instructions

La pile

•Les programmes possèdent des procédures et des

variables locales

•Où sont stockées les variables?

–à un emplacement déterminé: impossible (double

invocation)

–dans une zone mémoire nommée pile

•pas d'adresse absolue

•LV contient l'adresse de l'emplacement des variables

locales pour la procédure active

•SP l'adresse de la plus haute variable locale

•L'espace entre LV et SP stock les variables

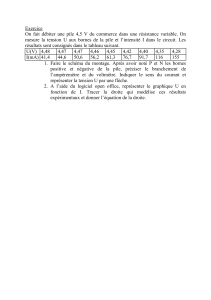

Appel de plusieurs procédures et pile

•La procédure A a 3 variables locales

•La procédure B a 4 variables locales

•La procédure C a 2 variables locales

•La procédure D a 5 variables locales

a)A est active b)Après appel de B par A c) Après appel de C par

B d) Après C et B et appel de D par A

La mémoire

est réutilisée

Autre utilisation de la pile

•Stocker des opérandes:

A1=A2+A3;

Push A2 sur

la pile Push A3 sur

la pile

Pop A2 et A3 de la

pile, addition et

Push le résultat

Pop du résultat

et stockage

dans A1

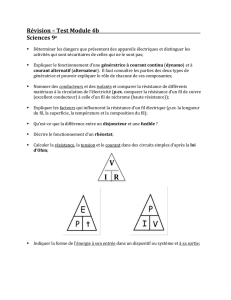

Le modèle mémoire IJVM

•Un tableau de 4 GByte ou 1 Gword

•Les instructions IJVM accèdent la mémoire

en indexant depuis des pointeurs

Constantes Variables

locales

Opérandes

Programme

Adressage par octetsAdressage par mots

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

1

/

22

100%