Bascule pour diviser la fréquence par 2

ê

■uropaisches Patentamt

ïuropean Patent Office

Dffice européen des brevets

2> Numéro de publication: D 336 460

M

2) DEMANDE DE BREVET EUROPEEN

© Numéro de dépôt: 89200401.1

g) Date de dépôt: 20.02.89

© Int. Cl.4: H03K 3/037 , H03K 3/356

© Priorité: 26.02.88 FR 8802374

@ Date de publication de la demande:

11.10.89 Bulletin 89/41

© Etats contractants désignés:

DE FR GB IT

") Demandeur: RTC-COMPELEC

117, quai du Président Roosevelt

F-92130 Issy les Moulineaux(FR)

g) FR

Demandeur: N.V. Philips'

Gloeilampenfabrieken

Groenewoudseweg 1

NL-5621 BA Eindhoven(NL)

g) DE GB IT

g) Inventeur: Chantepie, Bernard

Société Civile S.P.I.D. 209, rue de l'Université

F-75007 Paris(FR)

© Mandataire: Lemoyne, Didier et al

S.P.i.D. 209, rue de l'Université

F-75007 Paris(FR)

© Bascule pour diviser la fréquence par 2.

© Bascule (40) pour diviser par 2 la fréquence d'un

signal appliqué à une borne d'entrée (CK), compre-

nant une bascule RS (60) constituée par une premiè-

re (61) et une deuxième (62) portes logiques dont

les premières entrées sont mutuellement intercou-

plées à leurs sorties (Oi,02). Selon l'invention, la

bascule (40) comprend également une troisième

f-(20a) et une quatrième (20b) portes logiques dont

^les sorties (Oa,Ob) sont couplées, respectivement,

Qaux entrées (h ,l2) de la première (61) et la deuxième

CO(62) portes logiques, et dont les premières entrées

^"sont couplées, respectivement, à la sortie (02,Oi) de

jQla seconde (62) et de la première (61) portes logi-

Cîques, via, respectivement, un chemin de conduction

^d'un premier (30a) et d'un second (30b) interrup-

Oteurs' les secondes entrées de la troisième (20a) et

«de la quatrième (20b) portes logiques et l'entrée

2j(Ga,Qb) des interrupteurs (30a,30b) étant reliées à

ladite borne d'entrée (CK).

Application aux circuits intégrés numériques LSI.

nu. i

xerox uopy centre

I =P 0 336 460 A1

3 ASCII LE POUR DIVISER LA FREQUENCE PAR 2.

La présente invention concerne une bascule

30ur diviser par 2 la fréquence d'un signal appliqué

à une borne d'entrée, comprenant une bascule RS

instituée par une première et une deuxième por-

tes logiques dont les premières entrées sont mu-

tuellement intercouplées à leurs sorties.

L'invention trouve une application particulière-

ment avantageuse dans le domaine des circuits

intégrés numériques LSI.

On connaît de l'article "Selectively Doped He-

terostructure Frequency Dividers" (IEEE Electron

Device Letters, Vol. 4, n°10, Oct. 1983) une bas-

cule pour diviser la fréquence par 2 appelée bas-

cule D. Cette bascule connue présente, outre un

second étage représenté par la bascule mention-

née dans le préambule, un premier étage compre-

nant 4 portes NOR dont une à 3 entrées. La

bascule connue de l'état de la technique comporte

donc au total 6 portes NOR à 2 ou 3 entrées, ce

qui représente 14 transistors et 6 résistances, pour

une consommation de 1,5 mW environ à 1 GHz,

lorsque les transistors sont des MESFET à enri-

chissement (appelés aussi N-off pour Normaily-off).

Le problème technique très général à résoudre

lorsque l'on veut réaliser des circuits numériques

devant être intégrés à grande échelle (LSI) est de

diminuer le nombre de composants des ensembles

assurant une fonction donnée, comme, par exem-

ple, les portes logiques d'une bascule D. D'autre

part, c'est également un souci constant que de

chercher à réduire la consommation des circuits.

Enfin, ces résultats doivent, de préférence, être

obtenus sans altération des performances, et, en

particulier, de ia dynamique.

Aussi le problème technique à résoudre par

l'objet de ia présente demande est de proposer

une bascule pour diviser par 2 la fréquence d'un

signai appliqué à une borne d'entrée, comprenant

une bascule RS constituée par une première et

une deuxième portes logiques dont les premières

entrées sont mutuellement intercouplées à leurs

sorties, bascule qui serait formée d'un nombre de

composants moins élevé que la bascule D connue,

et dont la consommation serait plus faible, tout en

présentant la même fréquence maximum de fonc-

tionnement.

La solution au problème technique posé

consiste, selon la présente invention, en ce que la

bascule comprend également une troisième et une

quatrième portes logiques dont les sorties sont

couplées, respectivement, aux entrées de la pre-

mière et la deuxième portes logiques, et dont les

premières entrées sont couplées, respectivement,

à la sortie de la seconde et de la première portes

logiques, via, respectivement, un chemin de

conduction d un premier et d un second interrup-

teurs, les secondes entrées de la troisième et de la

quatrième portes logiques et l'entrée des interrup-

teurs étant reliées à ladite borne d'entrée.

5 Ainsi, la bascule conforme à l'invention est

constituée de 1 0 transistors et de 4 résistances, ce

qui représente une diminution appréciable du nom-

bre de composants. D'autre part, lorsque les tran-

sistors sont des MESFET à enrichissement, la De-

10 manderesse a constaté une diminution de moitié

(0,75 mW) de la consommation à 1 GHz. En outre,

la fréquence maximum de la bascule selon l'inven-

tion est la même (Fmax = 1/4Tpd, où Tpd est le

temps de propagation à travers une porte) que la

75 bascule de l'état de la technique.

La description qui va suivre en regard du des-

sin annexé, donné à titre d'exemple non limitatif,

fera bien comprendre en quoi consiste l'invention

et comment elle peut être réalisée.

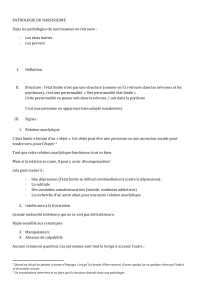

20 La figure 1 est le schéma d'une bascule

pour diviseur de fréquence par 2 selon l'invention.

La figure 1 donne le schéma d'une bascule 40

pour diviser par 2 la fréquence d'un signal appliqué

25 à une borne d'entrée CK, comprenant une bascule

RS 60, connue en soi, constituée par une première

61 et une deuxième 62 portes NOR dont les pre-

mières entrées sont mutuellement intercouplées à

leurs sorties Oi, O2. Comme le montre la figure 1,

30 la bascule 40 comprend également une troisième

20a et une quatrième 20b portes NOR dont les

sorties Oa, Ob sont couplées, respectivement, aux

entrées h , I2 de la première 61 et de la deuxième

62 portes NOR de la bascule RS 60. D'autre part,

35 les premières entrées des troisièmes 20a et qua-

trième 20b portes NOR sont couplées, respective-

ment, à la sortie O2, d de la seconde 62 et de la

première 61 portes NOR via, respectivement, un

chemin de conduction d'un premier 30a et d'un

4Q second 30b interrupteurs constitués par des tran-

sistors MESFET AsGa à enrichissement. Enfin, les

secondes entrées de la troisième 20a et de la

quatrième 20b portes NOR et l'entrée Ga, Gb des

transistors 30a, 30b étant reliés à la borne d'entrée

45 CK.

L'ensemble de ia porte NOR 20a

(respectivement 20b) et du transistor 30a

(respectivement 30b) constitue un élément de mé-

moire 10a (respectivement 10b) du type maltre-

50 esclave avec remise à zéro de l'esclave. En effet,

sur l'exemple de l'élément 10a :

- lorsqu'on applique en Ga un niveau logique 1, la

sortie Oa est à 0. Pendant cette opération, la

capacité Cgs intrinsèque du transistor MESFET

(jouant le rôle de maître), qui se trouve à la pre-

2

3 EP 0 336 460 A1

-nière entrée de la porte NOR 20a flouant le rôle

j'esclave), se charge et le niveau logique (E) de

'entrée Sa se retrouve ainsi sur la première entrée,

• lorsqu'on applique en Ga un niveau logique 0, on

Dince le transistor 30a, le niveau logique en Sa ne

oeut passer sur la première entrée. La porte NOR

sffectue son opération entre 0 et le niveau logique

sur la première entrée, c'est à dire le niveau logi-

que (E) qui existait en Sa lors de la phase précé-

dente. On retrouve donc E à la sortie Oa de la

porte NOR.

L'ensemble de la bascule de la figure 1 est

réalisée avec des transistors MESFET à enrichis-

sement, dont la tension de seuil VT est de 0,2 V et

la transconductance gm de 200 mS/mm. Ils fonc-

tionnent avec un courant lDs de 5,7 mA environ

pour une largeur W de 100 u.m et avec VGS = 0,7 V,

VDS = 2 V et une longueur de grille de 0,7 um.

Les deux transistors 30a et 30b ont une largeur

de 5 um. Les portes 20a, 20b sont constituées par

des transistors de 1,5 um de large et par une

résistance de 3,5 kîî. Les portes 61 et 62 sont

composées de transistors de 20 um de large et

d'une résistance de 2,5 kQ.

Bien qu'il n'a été fait mention dans ce texte

que de transistors MESFET, d'autres types de tran-

sistors peuvent être envisagés, comme, par exem-

ple, des transistors MOSFET ou bipolaires. De

même, bien que le mode de réalisation décrit com-

prend des portes NOR et des MESFET à canal n,

l'homme du métier serait capable de déduire les

modes de réalisation correspondants comprenant

des portes NAND.

Revendications

1 . Bascule (40) pour diviser par 2 la fréquence

d'un signal appliqué à une borne d'entrée (CK),

comprenant une bascule RS (60) constituée par

une première (61) et une deuxième (62) portes

logiques dont les premières entrées sont mutuelle-

ment intercpuplées à leurs sorties (Oi ,02), caracté-

risée en ce que la bascule (40) comprend égale-

ment une troisième (20a) et une quatrième (20b)

portes logiques dont les sorties (Oa.Ob) sont cou-

plées, respectivement, aux entrées (I1J2) de la pre-

mière (61) et la deuxième (62) portes logiques, et

dont les premières entrées sont couplées, respecti-

vement, à la sortie (02,0i) de la seconde (62) et

de la première (61) portes logiques, via, respective-

ment, un chemin de conduction d'un premier (30a)

et d'un second (30b) interrupteurs, les secondes

entrées de la troisième (20a) et de la quatrième

(20b) portes logiques et l'entrée (Ga,Gb) des inter-

rupteurs (30a,30b) étant reliées à ladite borne d'en-

trée (CK).

2. Bascule selon la revendication 1, caractéri-

sée en ce que chaque porte logique

(61 ,62,20a,20b) est une porte NOR, lesdits inter-

rupteurs (30a,30b) étant des transistors à effet de

; champ à enrichissement.

<o

'5

20

25

30

35

40

45

50

3

EP 0 336 460 A1

PHF 88-508

ê

Office européen g^ppQ^

DE RECHERCHE EUROPEENNE Numer0 "e h "

des brevets

EP 89 20 0401

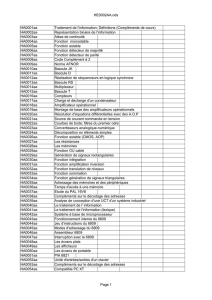

DOCUMENTS CONSIDERES COMME PERTINENTS

, . Citation du document avec indication, en cas de besoin, Revendication CLASSEMENT DE LA

oategone des parties pertinentes concernee DEMANDE (Int. CI.4)

A FR-A-2 362 534 (LABORATOIRES 1 „ n, „ ,/nr7

D'ELECTRONIQUE ET DE PHYSIQUE APPLIQUEE H 03 K 3/356

* figure 1, reperes 12,22,11,21 et

connexions (X-Y) et (X-Z); page 1,

lignes 1-9; page 3, ligne 11 - page 5,

Hgne 9; figure 4 *

A * page 4, lignes 12-17 * 2

A PATENT ABSTRACTS OF JAPAN 1

vol. 6, no. 107 (E-113)(985), 17 juin

1982; & JP - A - 57 37934 (TOKYO

SHIBAURA DENKI K.K.) 02.03.1982

A PATENT ABSTRACTS OF JAPAN 1

vol. 5, no. 44 (E-50)(716), 24 mars

1981; & JP - A - 56 747 (TOKYO SHIBAURA

DENKI K.K.) 07.01.1981

A DD-A- 247 558 (TECHNISCHE 1

UNIVERSITAET DRESDEN) domaines techniques

* fiaures 2.3: abreae * recherches an.. ci.4)

D,A IEEE ELECTRON DEVICE LETTERS 1 J °3 K 3/037

vol. EDL-4, no. 10, octobre 1983, pages H 03 K 3/3bb

377-379; R.A. KIEHL et al . -."Selectively

doped heterostructure frequency

dividers" * figure 1 *

A CH-A- 524 933 (CENTRE ELECTRONIQUE 1

H0RL0GER S.A.)

* figures 1,3 *

Le present rapport a ete etabli pour toutes les revendications

Lien de la recherche

BERLIN

Date d achèvement de la recherche

30-05-1989

ucaminaieur

ARENDT M

CATEGORIE DES DOCUMENTS CITES

X : particulièrement pertinent à lui seul

Y : particulièrement pertinent en combinaison avec un

autre document de ia même catégorie

A : arrière-plan technologique

O : divulgation non-écrite

P : document intercalaire

T : théorie ou principe a la base de l'invention

E : document de brevet antérieur, mais publié à la

date de dépôt ou après cette date

D : cité dans la demande

L : cité pour d'autres raisons

& : membre de la même famille, document correspondant

6

6

1

/

6

100%